# UNIVERSITA' DEGLI STUDI DI PAVIA

## DIPARTIMENTO DI ELETTRONICA

#### DOTTORATO DI RICERCA IN MICROELETTRONICA

# CMOS PIXEL SENSORS AND MIXED-SIGNAL READOUT ELECTRONICS IN A 3D INTEGRATION TECHNOLOGY

Tutor: Prof. Valerio Re

Coordinatore del Dottorato: prof. Rinaldo Castello

> Tesi di Dottorato di Luigi Gaioni

Anno Accademico 2008/2009

# Ringraziamenti

Desidero ringraziare il prof. Valerio Re, mio tutor nel presente lavoro di ricerca, già mio relatore di tesi di laurea, per i suoi preziosi insegnamenti, per tutte le opportunità che mi ha offerto, per i consigli e per tutto il tempo a me dedicato nel corso di questi utlimi anni.

Ringrazio con sincero affetto la prof. Valeria Speziali per essermi sempre stata vicina, per tutti i suggerimenti e tutta l'attenzione che ha avuto nei miei confronti.

Sarò sempre grato a Massimo Manghisoni, Enrico Pozzati, Lodovico Ratti e Gianluca Traversi per i costanti consigli, la pazienza e la disponibilità: di loro sono debitore di molte delle conoscenze acquisite durante questi anni.

Doveroso, infine, ringraziare Fabio, Marco, Claudio, Alessia, Stefano, Emanuele e Valentina per la pazienza con la quale hanno sopportato Bach. ii

# Contents

| Intro | duction | L |

|-------|---------|---|

|       |         |   |

| 1        | $\mathbf{Thr}$ | ee dimensional integrated circuits             | <b>5</b>  |

|----------|----------------|------------------------------------------------|-----------|

|          | 1.1            | Motivation for 3D ICs                          | 6         |

|          | 1.2            | Benefits of 3D ICs                             | 7         |

|          |                | 1.2.1 Power and performance                    | 8         |

|          |                | 1.2.2 Density $\ldots$                         | 8         |

|          |                | 1.2.3 Functionality                            | 9         |

|          | 1.3            | MAPS sensors: from 2D to 3D                    | 9         |

|          | 1.4            | 3D IC fabrication technology                   | 12        |

|          |                | 1.4.1 Chip stacking                            | 13        |

|          |                | 1.4.2 Transistor stacking                      | 14        |

|          |                | 1.4.3 Die-on-Wafer stacking                    | 15        |

|          |                | 1.4.4 Wafer-level stacking                     | 16        |

|          | 1.5            | Tezzaron's 3D solution                         | 17        |

|          | 1.6            | MITLL's 3D solution                            | 22        |

|          |                |                                                |           |

| <b>2</b> | Cha            | aracterization of a 180 nm CMOS SOI Technology | <b>25</b> |

|          | 2.1            | SOI MOSFETs                                    | 26        |

|          | 2.2            | Investigated devices                           | 29        |

|          | 2.3            | Static measurements                            | 30        |

|          | 2.4            | Noise measurements                             | 34        |

|          | 2.5            | Analysis of static measurement results         | 38        |

|          | 2.6            | Analysis of noise measurement results          | 41        |

|          |                | 2.6.1 White noise                              | 41        |

|          |                | 2.6.2 $1/f$ noise                              | 44        |

|          |                | 2.6.3 Lorentzian-like noise                    | 46        |

|          | 2.7            | Conclusions                                    | 47        |

1

| 3  | The   | sparsified data readout (                | SDR1) chip          |            |  | <b>49</b> |

|----|-------|------------------------------------------|---------------------|------------|--|-----------|

|    | 3.1   | Specifications for ILC                   |                     |            |  | 50        |

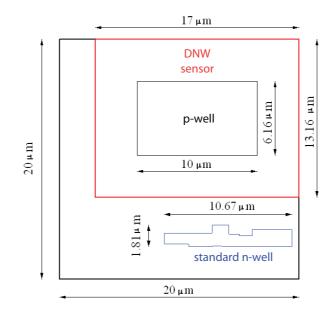

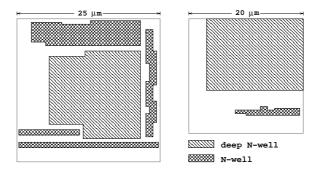

|    | 3.2   | Deep n-well MAPS sensors                 |                     |            |  | 54        |

|    | 3.3   | The SDR1 chip $\ldots$ $\ldots$ $\ldots$ |                     |            |  | 56        |

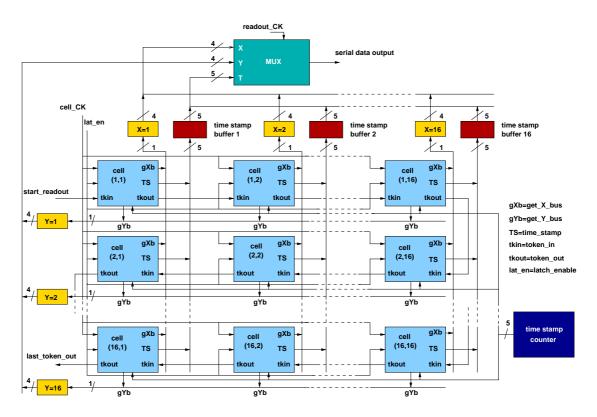

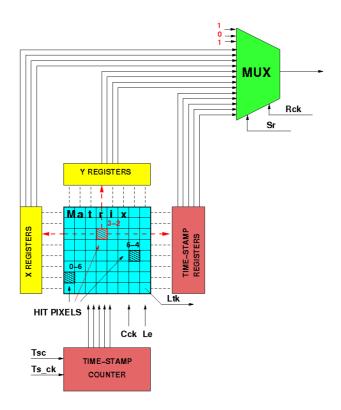

|    | 3.4   | Readout architecture                     |                     |            |  | 58        |

|    |       | 3.4.1 Detection phase                    |                     |            |  | 59        |

|    |       | 3.4.2 Readout phase                      |                     |            |  | 60        |

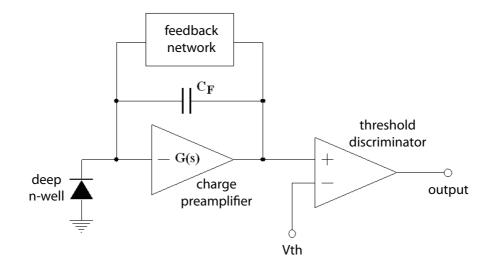

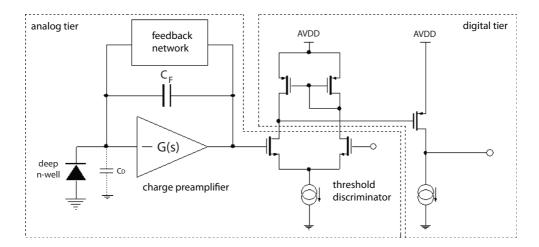

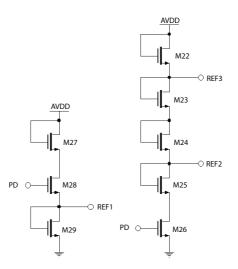

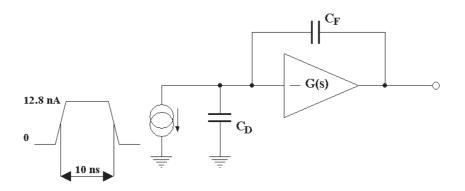

|    | 3.5   | Analog front-end                         |                     |            |  | 61        |

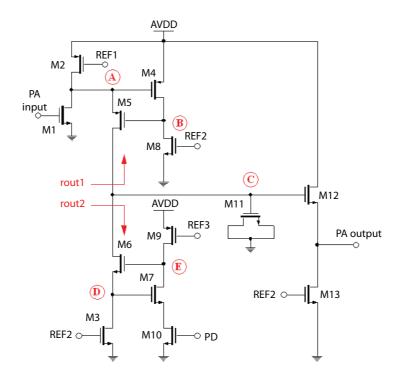

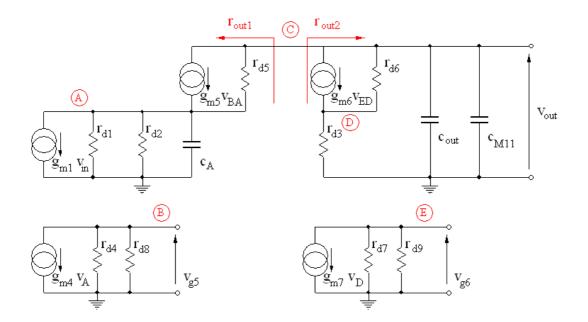

|    |       | 3.5.1 Charge preamplifier                |                     |            |  | 62        |

|    |       | 3.5.2 Reset operation                    |                     |            |  | 70        |

|    |       | 3.5.3 Threshold discrimina               | tor                 |            |  | 73        |

|    |       | 3.5.4 Analysis of the discri             | minator threshold   | dispersion |  | 74        |

|    | 3.6   | Design criteria for analog pr            | ocessor             |            |  | 77        |

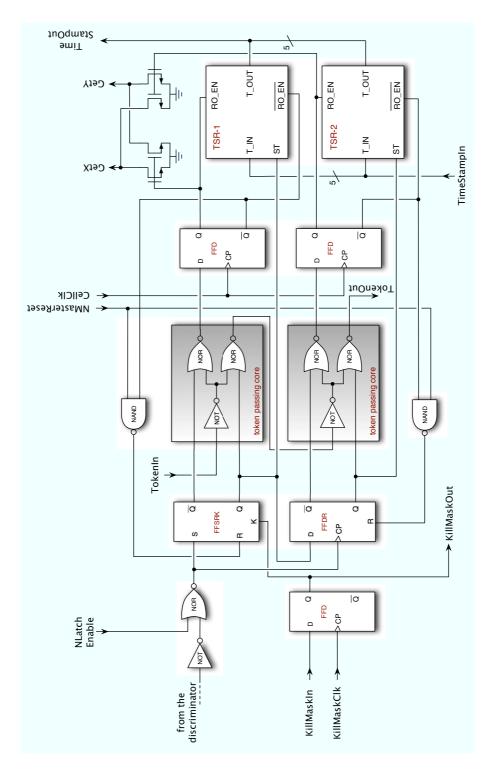

|    | 3.7   | Digital front-end                        |                     |            |  | 78        |

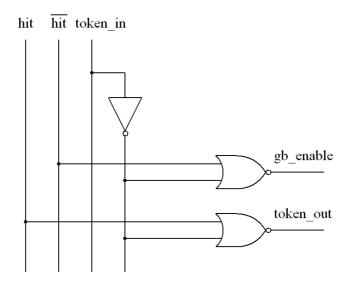

|    |       | 3.7.1 Token passing core .               |                     |            |  | 81        |

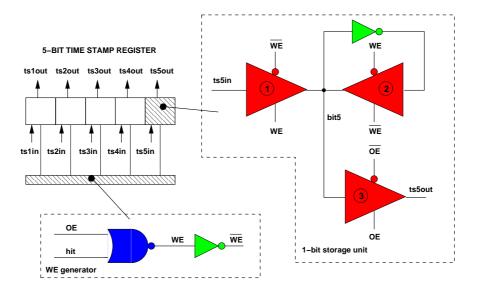

|    |       | 3.7.2 Time stamp register                |                     |            |  | 82        |

|    |       | 3.7.3 Kill Mask                          |                     |            |  | 83        |

|    | 3.8   | Digital back-end                         |                     |            |  | 83        |

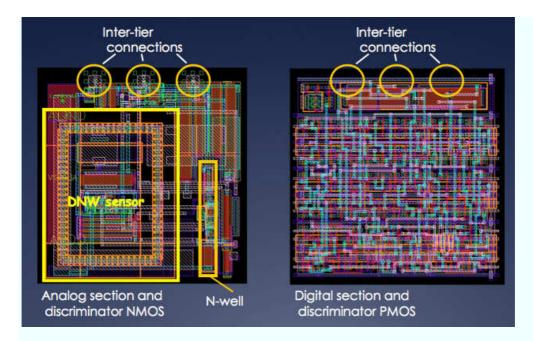

|    | 3.9   | Geometrical features of the              |                     |            |  | 84        |

|    | 3.10  | Cell layout                              |                     |            |  | 85        |

|    | 3.11  | Circuit simulation results .             |                     |            |  | 86        |

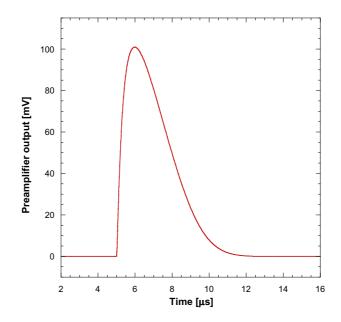

|    |       | 3.11.1 Analog front-end                  |                     |            |  | 86        |

|    |       | 3.11.2 Equivalent noise cha              |                     |            |  | 87        |

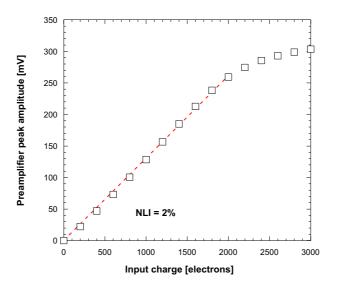

|    |       | 3.11.3 Charge sensitivity an             |                     |            |  | 90        |

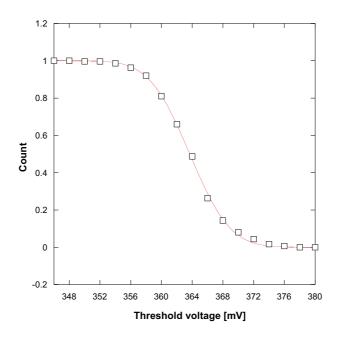

|    |       | 3.11.4 Threshold dispersion              |                     |            |  | 91        |

|    | 3.12  | Digital sections                         |                     |            |  | 93        |

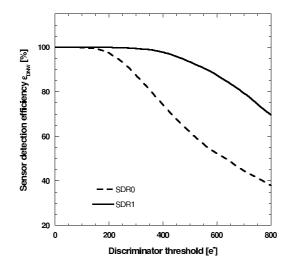

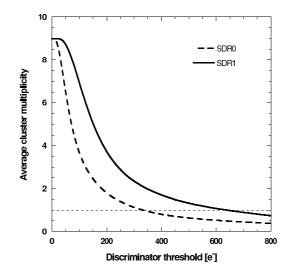

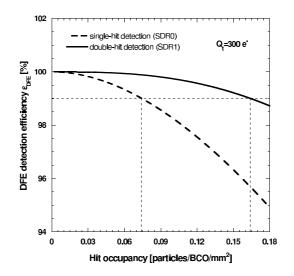

|    |       | Detection efficiency                     |                     |            |  | 101       |

|    |       | 3.13.1 Sensor detection effic            |                     |            |  | 102       |

|    |       | 3.13.2 Digital front-end det             | ection efficiency . |            |  | 104       |

|    | 3.14  | Structures integrated in the             | SDR1 chip           |            |  | 105       |

|    |       |                                          |                     |            |  |           |

| Co | onclu | sions                                    |                     |            |  | 108       |

| Bi | bliog | raphy                                    |                     |            |  | 109       |

iv

### Introduction

The continued reduction of microelectronic device size over the past few decades has led to pioneering improvements in performance of electronic products. This miniaturization has been associated with unrelenting improvements in process technologies. Beside the evident benefits introduced by the scaling process, such as high level of integration density, there are also some other aspects which have to be considered. Smaller feature sizes imply lower supply voltages, sharply increasing mask costs, and larger gate leakage currents. Moreover, small feature size technologies also have to cope with increasing interconnect density and delays. Now, perhaps, the semiconductor industry is approaching a domain where physics makes it difficult to achieve smaller gate technologies. This scenario has led to consideration of alternative arrangements of electronics based on vertical interconnection of layers of circuitry. These technologies, usually referred to as "3D", rely on layering tiers of active circuitry interconnected to each other. A vertically interconnected wafer, in addition to having increased overall circuit density, reduces the overall length of the device interconnections, increasing the speed by reducing resistance, inductance and parasitic capacitance. Power consumption is also decreased due to the reduced wire length and smaller capacitance. In addition, the layers may be fabricated in different technologies, each optimized for a particular application. A variety of integration technologies for 3D integrated circuits (IC) have been demonstrated. Silicon-on-Insulator (SOI) technology is particularly appealing in these processes.

This thesis work discusses the 3D integration of CMOS monolithic active pixel sensors (MAPS). MAPS sensors represent nowadays a promising alternative

with respect to other mature technologies in different sectors. Initially conceived for imaging application, in competition to CCD devices, CMOS MAPS with simple readout schemes have gained a significant share of the consumer electronic, market where they are used in such commercial devices as videocameras or cameras for digital still photography. Vertical integration process capabilities make it possible to fabricate compact 3D MAPS detectors in which the different sections included in a traditional pixel (e.g. the sensing element, the analog front-end, digital processing blocks and so on) can be split into different layers, each optimized for the particular function accomplished by the layer itself, with significant benefits in terms of pixel size and functionality. Moreover, CMOS MAPS have been proposed in the last years as suitable candidates for charged particle trackers at the next generation colliders like International Linear Collider (ILC) and Super B-Factory as alternative tracking devices with respect to hybrid pixel detectors. MAPS devices, indeed, may comply with the severe constraints set by the future experiments at these colliders, which require highly granular and low mass detectors. CMOS MAPS are adequate in terms of material budget, since their sensing element shares the same substrate with the readout electronics; furthermore, substrate thickness can be reduced to a few tens of microns with no significant signal loss. The proposed 3D MAPS, object of this thesis works, involves the use of a deep n-well/p-substrate junction, provided by triple-well CMOS technologies, as collecting element. In this way, the sensor can be extended to cover a large area of the pixel cell. This solution, inherited from the so called deep n-well MAPS (DNW MAPS) fabricated in planar (2D) technologies, allow designers to realize more complex readout circuits, taking advantage of fully CMOS architectures: the effects of charge collection from PMOS n-wells, which acts as competitive electrodes against the main collecting electrode, may be significantly limited. Vertical integration processes, by stacking two or more layers one on the top of the other, make it possible to reduce interaction effects between different sections of the pixel cell and may also improve collection efficiency since PMOS wells can be placed in a different layer with respect to the sensor.

The first chapter introduces the 3D integration process, the benefits related to this technology and the main approaches involved in 3D IC fabrication. At the end of the chapter, a brief overview of the Tezzaron Semiconductor and MIT Lincoln Laboratory processes will be provided: these processes, indeed, are those employed in the design and fabrication of the devices subject of this thesis work. The second chapter provides the static, signal and noise characterization of devices fabricated in a 180 nm SOI technology suitable for 3D

#### INTRODUCTION

integration.

The third chapter discusses the features of a new kind of DNW MAPS, called SDR1 (Sparsified Data Readout), which exploits the capabilities of vertical integration processing in view of the design of high granularity detectors. SDR1 inherits and extends the functional capabilities of DNW MAPS fabricated in planar CMOS technology and is expected to show better performance with respect to 2D versions.

INTRODUCTION

# Chapter 1

# Three dimensional integrated circuits

Over the last years, CMOS scaling has made it possible to comply with the demand of the computer and information technology industry, that is, very large scale integrated (VLSI) circuits with increasing functionality and performance at minimum cost and power dissipation. In planar (2D) technologies, scaling is reducing gate delays but also increasing interconnect ones: interconnect density turns out to be increased in the design of microelectronic circuits realized with small feature sizes technologies. Increasing interconnect density affects the power consumption in high-performance 2D chips, where a significant fraction of the total chip power consumption can be due to the wiring network used for clock distribution, which is usually realized using long global wires. Another aspect which has to be taken into account is represented by the impact of the interconnect scaling on the traditional computer-aideddesign (CAD) methodologies and tools, which are causing the design cycles to increase, thus increasing the time-to-market and the cost per chip function. Furthermore, increasing drive for the integration of disparate signals (digitals, analog, RF) and technologies (SOI, SiGe HBTs, GaAs, and so on) is introducing various system-on-a-chip (SoC) design concepts, for which existing planar (2D) technologies may not be suitable. In order to overcome critical issues related to 2D designs, dozens of companies and organizations are working on 3D integrated circuits in the United States, Europe and Asia: companies such as IBM, Intel, Philips, STM, Tezzaron Semiconductor and Samsung, and organizations such as MIT Lincoln Labs and Fraunhofer Institute IZM-Munich are very active in 3D. Each of them has its own approach to working on the key technologies needed for 3D. A review of the options for the 3D integration

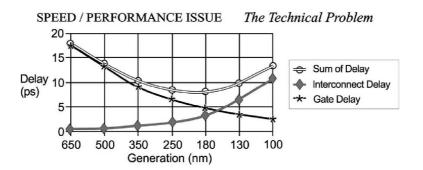

Figure 1.1: Gate and interconnect delays as a function of gate technology.

is presented in the next sections; also, a brief description of the methods employed by Tezzaron and MIT Lincoln Labs, whose technology processes have been involved in this thesis work, will be presented at the end of this chapter.

#### 1.1 Motivation for 3D ICs

Because of advances in IC technology, such as lithography, etching and reduction in defect density, which have led to fabrication of very small feature size devices, 2D chip size is continually increasing [1]. This is due to the increase in chip complexity required to satisfy the ever-growing demand for functionality and higher performance, which in turn requires more and more transistors to be closely packed and connected. Although smaller feature sizes have improved device performance [2], the miniaturization process has led to less positive consequences in terms of performance of interconnect wires. Indeed, smaller wire cross sections, smaller wire pitch, and longer lines running along the chips have increased the resistance and the capacitance of these lines resulting in a significant increase in signal propagation (RC) delay. In particular, as interconnect scaling continues, RC delay represents the dominant factor determining the performance of advanced ICs [3]. At 250 nm technology node, copper with low-k dielectric was introduced in order to limit the effect of increasing interconnect delay [4]. Fig. 1.1 shows the rapid increase in delay time caused by the interconnect loading. It is possible to notice how, beyond the 180 nm regime, interconnect delays affect the benefits introduced by small feature size devices and by the use of new materials in ICs fabrication. Nonetheless, more scaled technologies employing low-k dielectric has been realized, even if these processes turn out to be quite expensive.

Three-dimensional integrated circuits, which contain multiple layers of active devices, extensively utilize the vertical dimension to connect components and are expected to address interconnect delay related problems and to enable integration of heterogeneous technologies [5],[6]. It can be shown that 3D architectures can reduce the overall global wire-length, while increasing the number of local wires [7]. Moreover, the decrease in the number of long interconnects could directly translate to an increase in device density, provided that the devices are efficiently packed, placed, and wired. Another interesting feature is the fact that the 3D architecture lends itself to the realization of a SoC.

SoC is a broad concept that refers to the integration of nearly all aspects of a system design on a single chip. These chips are often mixed-signals and/or mixed-technology designs, including such diverse combinations as analog, RF, low-power logic and embedded DRAM.

There is a plethora of 3D integration techniques in literature, but the most appealing and competitive schemes to date are those involving either lowtemperature silicon epitaxy or wafer bonding. A brief review of the technology options for 3D fabrication will be presented in the following sections.

#### 1.2 Benefits of 3D ICs

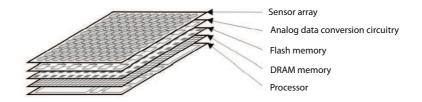

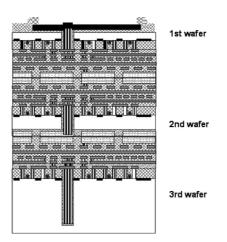

In the 3D design, an entire (2D) chip is divided into a number of blocks, and each block is placed on a separate layer of silicon that are stacked on top of each other, as schematically shown in Fig. 1.2. The 3D architecture offers extra flexibility in system design, placement, and routing, reducing the earlier discussed negative impact of deep-submicrometer interconnects on VLSI design. Other benefits of 3D ICs include improved packing density, noise immunity,

Figure 1.2: A possible design for a 3D Soc.

improved total power due to reduced wire length and lower capacitance, and the ability to implement added functionality. Furthermore, the 3D chip design technology may be exploited to build SoC by placing circuits with different voltage and performance requirements in different layers.

#### 1.2.1 Power and performance

The effects associated with long interconnect paths in 2D chips are mitigated by the use of short wires in 3D designs. These shorter wires will decrease the average load capacitance and resistance and decrease the number of repeaters which are needed to regenerate signal on long wires. A significant portion of the total power consumption is indeed due to interconnect wires with their supporting repeaters: 3D ICs, reducing the average interconnect length with respect to 2D counterparts, will improve wire efficiency (about 15%) and reduce total active power by more than 10% [8]. Moreover, dynamic power consumption is in the charging and discharging of the interconnect capacitance. The RC delay of signals ultimately limits the maximum speed of a circuit; this delay increases as the square of the wire's length l. The experimental derived forumla is:

$$t_d = 0.35 \ r \ c \ l^2. \tag{1.1}$$

Since resistance (r) and capacitance (c) per unit length are increasing with the scaling process, by means of 3D technology is it possible to reduce propagation delay by reducing the wire length l.

Also, regenerative repeaters used in CMOS circuits to restore signal on long wires, may introduce noise through the substrate: reducing the number of the repeaters makes it possible to curb this effect. Moreover, the shorter interconnects in 3D ICs, with the consequent reduction of load capacitance and the lower wire-to-wire capacitance, will reduce the noise due to simultaneous switching events and the noise coupling between signal lines.

#### 1.2.2 Density

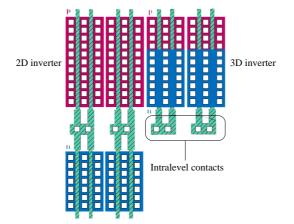

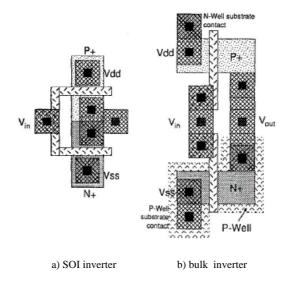

By adding a third dimension to the conventional two-dimensional device layout, the transistor packing density is improved, thereby allowing a reduced chip footprint. As an example, Fig. 1.3 compares layout designs of 2D and 3D inverters: it is possible to notice the area gain for the 3D design. When the total layout area (the sum of the device area and the metal routing area) is compared for 2D and 3D standard cells with different inverter designs, a 30% areal gain for the 3D cells can be achieved [9]. The ability to stack circuit elements, thus shrinking the footprint and potentially reducing the volume and/or the weight of a chip, is particularly appealing for wireless or portable electronics, where silicon real estate is at a premium. Reduced chip volume and weight are also motivated by military applications.

Figure 1.3: 2D and 3D inverter layout.

#### 1.2.3 Functionality

Many of the general techniques for building 3D ICs will facilitate the integration of heterogeneous materials, devices, and signals and enable flexibility in device structure, system design, and routing, making it possible to integrate an entire system onto a single piece of silicon and to implement added functionality in a single 3D chip.

#### 1.3 MAPS sensors: from 2D to 3D

Silicon devices have been used since the 1960s for the detection of radiation [10]. In the early 1990s monolithic pixel sensors have been proposed as a viable alternative to CCD's in visible imaging. These sensors are made in a standard VLSI technology, usually CMOS: in the literature, they are normally referred to as CMOS sensors.

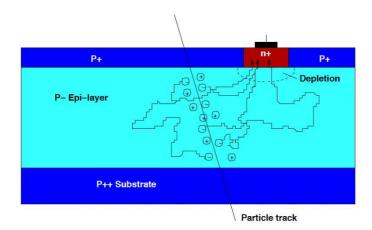

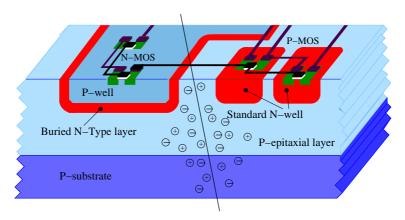

The cross-section view of Fig. 1.4 shows the basic principles underlying CMOS sensors. In most modern CMOS process, n- and p-wells are fabricated on top of a thin p-doped epitaxial layer, with resistivity of the order of 1-10  $\Omega$  cm. The epitaxial layer thickness ranges between a few and up to about 20  $\mu$ m and it is lightly doped with respect to the underlying p-substrate, whose main function is for mechanical support. A pn junction exists between the n-well and the p-epilayer and can be used as the detecting element. Because of the difference

Figure 1.4: Simiplified cross section of CMOS pixel with epitaxial layer .

in doping between the epitaxial layer and the p-well and the p-substrate, a potential difference of a few times kT/q is created. The epitaxial layer acts as a shallow potential well for the electrons, which are the minority carriers. Electrons created by the radiation diffuse in the epitaxial layer till they are close enough to the nwell/p-epi diode, where they experience an electric field. They are then collected by the diode.

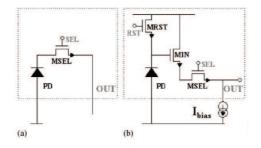

The first developments were based on the so-called Passive Pixel Sensors (see Fig 1.5 (a)). Only one selection transistor is integrated in the pixel together with the diode. The charge generated by the silicon/radiation interaction is integrated in the diode. The readout is performed by closing the selection switch and dumping the charge to a charge preamplifier, common to all the pixels in one column. This solution has the minimum amount of in-pixel electronics and thus has a very high fill factor, defined as the ratio between the detecting area and the total area of the pixel detector. It has however disadvantages in terms of speed and noise. The development of monolithic active pixel sensors (MAPS) was mainly pushed by the requirements of low power and low weight for space applications. In a MAPS pixel, an amplifier integrated in each cell directly buffers the charge signal. In the minimum configuration of a MAPS, three transistors (3-T) are integrated in the pixel, as shown in Fig. 1.5 (b). The transistor MRST is used to reset the pixel by dumping the integrated charge to the positive power supply line. The transistor MSEL is activated to select the readout of the pixel and MIN is the a source follower. The current source is common to all the pixels in one column. The diode is reverse biased by

Figure 1.5: (a) Schematic of a Passive Pixel Sensor (PPS). (b) Baseline, 3-MOS Active Pixel Sensor (APS).

connecting to  $V_{DD}$  through the reset switch; the charge-to-voltage conversion gain  $G_{in}$  at the input is given by  $1/C_{in}$ , where  $C_{in}$  is the total capacitance seen in the input node, and mainly determined by the diode capacitance and the gate-to-source capacitance of the input transistor. Typical values for the sensitivity  $G_{out}$  at the output of the source follower are in the range of 10-50  $\mu V/e^{-}$ .

Today most CMOS imagers have a MAPS structure for these main reasons:

- low cost, since they are fabricated in a standard VLSI technology;

- low power, since the circuitry in each pixel is active only during the readout and, contrary to CCD's, there is no clock signal driving large capacitances: the total power dissipation is usually in the range of 100mW for a few millions pixel device even with integrated analogue-to-digital conversion [11];

- random access, since each pixel can be addressed directly for readout;

- increased functionalities, taking advantage of the full capabilities of the CMOS technology: the control logic, the analogue-to-digital converter or other signal processing blocks can be integrated in the same substrate as the sensor array.

Because of these features, CMOS sensors are a candidate technology for demanding applications, which are typically found in space science. They also look attractive for particle tracking applications because of the following features:

- spatial resolution: a small pitch is achievable, and hence good spatial resolution even with a binary readout. Taking advantage of possible analogue readout and natural charge spread between neighbouring pixels, for very demanding application the spatial resolution can possibly be pushed down to less than 1 μm;

- low mass detectors: CMOS MAPS are adequate in terms of material budget, since their sensing element shares the same substrate with the readout electronics; furthermore, substrate thickness can be reduced to a few tens of microns with no significant signal loss;

- radiation tolerance, taking advantage of the reduced radiation sensitivity offered by nowadays submicron VLSI processes. [12]

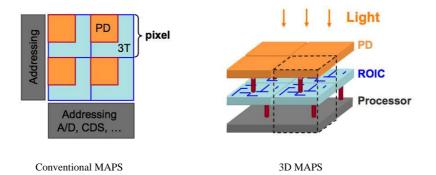

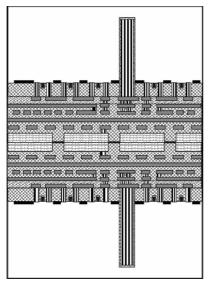

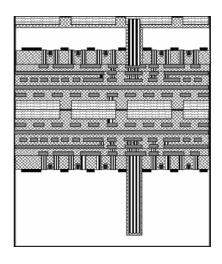

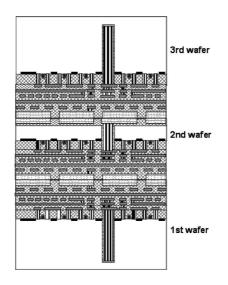

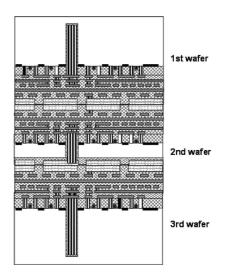

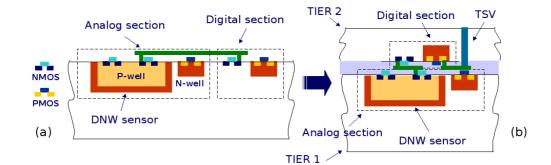

Anyway, the use of large area electrodes is strongly discouraged in 3T-MAPS design: indeed, increased capacitance would unacceptably degrade the noise figure and the charge sensitivity at the same time. In such sensor, in fact, charge sensitivity is inversely proportional to the parasitic capacitance of the collecting electrode and the equivalent noise charge (ENC), originating mainly from the reset operation, is proportional to the same capacitance. Moreover, in standard CMOS MAPS, use of PMOS devices in the design of the frontend electronics is avoided as the n-well they are integrated in might subtract charge to the collecting electrode leading to potentially serious efficiency loss. A possible 3D translation of a monolithic active pixel sensor is shown in Fig. 1.6. The figure displays the layout of a conventional MAPS device and its 3D counterpart, where the different sections of the 2D pixel cell have been placed in different layers. In the 2D version, pixel electronics and detector share the same area, whereas in the 3D case an ideal 100% fill factor is achievable. By placing analog and digital sections on a separate layer from the sensor, both N-channel and P-channel devices can be used in the circuit design. Moreover, the separation of the analog and digital layers provides a large amount of functionality in each pixel cell. Last, in the 3D version, the processing for each layer can be optimized by layer function.

#### 1.4 3D IC fabrication technology

3D ICs can be fabricated by means of four basic methods: chip stacking, transistor stacking, die-on-wafer stacking and wafer-level stacking. These four methods are described in this section. The most useful approaches for many applications, such as HEP (*High Energy Physics*) and imaging application, are

Figure 1.6: Comparison of MAPS and 3D pixel layout. In the 3D version, the photodetector (PD), the readout electronics (ROIC, more advanced with respect to the simple three-transistors, 3T, architecture employed in the 2D version) and the digital processing blocks are split into three different layers.

the last two, that is die-on-wafer and wafer-level stacking. These approaches share four common key technologies:

- bonding between layers using oxide to oxide fusion, copper tin eutectic bonding, or polymer bonding;

- wafer thinning using a combination of grinding, lapping, etching and CMP (*Chemical Mechanical Polishing*);

- through silicon vias (TSV) using different processes (some of which need to include hole passivation);

- high precision alignment of parts before bonding.

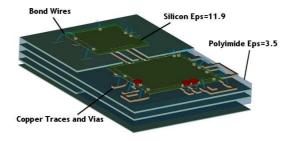

#### 1.4.1 Chip stacking

This method stacks fully processed and tested stand-alone components to produce a System-in-Package (SiP). SiP products are fully functional systems or sub-systems in an IC package format. SiP may contain one or more IC chips (wirebonded or flip chip) plus other components that are traditionally found on a system board such as surface mount discrete passive components, connectors, EMI shields and so on; a schematic view of a SiP is shown in Fig. 1.7. The only significant benefit offered by chip stacking is the reduction in system size. Indeed, connecting wires may be slightly shorter, but the achievable integration density is not different if compared with a planar system. In the same

Figure 1.7: Schematic view of a SiP.

way as standard 2D system, signals traveling from one layer to another must be pushed off-chip and then brought on-chip. Existing market uses for SiP include RF and wireless devices (such as power amplifiers, GPS modules, cellular, Bluetooth solutions), digital baseband solutions for the wireless markets and controllers for hard drives in the storage market. SiP technology can also be used to enhance single component packages that require improved circuit performance and reduced board real estate.

#### 1.4.2 Transistor stacking

This fabrication method makes it possible to create multiple levels of transistors on a single substrate. The success of this methodology is limited by thermal budget issues: copper or aluminum already laid down would be damaged by the temperatures required to build a new layer of transistors. Moreover, these temperatures could cause migration of transistor implants on other layers. Promising research on transistor stacking technologies has been performed by the Stanford University. Stanford's studies concern laser annealing and nickel nucleation. Laser annealing can be used for electrical activation of dopants without excessively heating material deeper within the work piece, making it possible to fabricate transistors on the upper levels of a general 3D structure without affecting the reliability of devices below [13]. Unfortunately, high defects density in these structures represents a problem. The nickel nucleation method allows to realize high quality multilayer structures at lower temperatures: nevertheless nickel ions can be kept in the structure, causing system failures. Matrix Semiconductor produces a highly successful variation on stacked transistors in its one-time programmable (OTP) memories [14]. This application turns out to be restricted only to special cases, and it can not be adopted in a large scale: indeed, this process doesn't provide the speed

Figure 1.8: Steps showing polymer bonding and via formation for die-to-wafer process.

or actual transistors required by most other devices.

#### 1.4.3 Die-on-Wafer stacking

In this method, system components are built on two semiconductor wafers. One wafer is diced: the singulated known good dies (KGDs) are aligned and bonded onto die sites of the second wafer. Dies can be attached to the host wafer by means of organic glues, oxide bonding or metal bonding. The resulting structure is further processed for thinning and formation of interconnects. In the die-on-wafer stacking approach interconnects can be made on the edge of the die, on the bonded faces themselves, or through-die. Depending on the type of interconnect, this method may realize a higher level of integration with respect to the chip-stacking one [15], with better cost per connection and higher interconnect density. The quality of die-on-wafer stacking is determined by the dies placement accuracy and therefore by the capabilities of the pickand-place equipment that positions each die on its wafer. Presently, placement accuracy is about 10  $\mu$ m, which limits the achievable density interconnect. Another issue which has to be taken into account is that the equipment cannot handle naked circuitry and so it does not protect adequately against static discharge. For this reason, the processed dies include protection structures which represent a cost in terms of power, speed, and die size. With die-onwafer approach, the parts may be bonded face to back (that is circuit side to

**Figure 1.9:** Face to face bond using  $Cu_3Sn$ .

substrate side) or face to face. Fig 1.8 shows a possible process sequence for device bonding and vias formation. Inter-device vias require to leave space in the design; if vias pass through a CMOS layer, they must be insulated from the substrate.

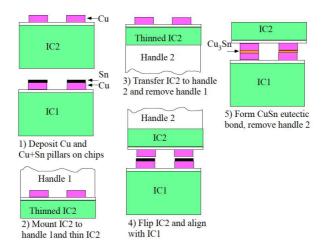

It is possible to realize face to face bonds by means of  $Cu_3Sn$  eutectic bond for both the electrical and mechanical connections between devices. The process for the Cu/Sn bond is shown in Fig. 1.9: a double handle transfer is needed as shown in steps 2 and 3.

#### 1.4.4 Wafer-level stacking

16

This last method bonds entire wafers into a stack. Wafers are frequently bonded together using an  $SiO_2$  bond. For good bonding, the wafers must be very flat and the surfaces must be extremely clean. As in die-on-wafer stacking, alignment accuracy, which is better in wafer-level stacking, determines the interconnect density. Technology processes provided by Tezzaron Semiconductor can achieve alignment of less than a micrometer. Wafer-level stacking supports a lower cost per connection and better interconnects density than die-on-wafer approach, because of the greater alignment accuracy and higher degree of surface planarity. As in the case of die-on-wafer stacking, process temperatures limit the use of mixed substrates: high temperatures, indeed, cause misalignment due to unequal expansions between mixed-wafer pairs. In wafer-level approach, all processing is done at the wafer level: wafer handling equipment protects against static discharge, so I/O buffering between layer is not required. Moreover, standard lithography and processing techniques, with few added process steps, can be used in structures fabrication with the wafer-level stacking. Bonding between wafer, as in the die-on-wafer method, can be made by means of organic gluing, oxide bonding and metal bonding. Each bonding technique has its benefits and drawbacks. Organic glue bonding reduces the possibility of particle contamination, but it does not provide a good metal interconnect. Oxide bonding makes it possible to improve alignment accuracy because of the room temperature prebonding process, but again it does not have an intrinsic metal connection. Metal bonding provides the interconnect, but alignment turns out to be more difficult because of the higher temperatures needed (about 400°C). Wafer-level stacking techniques are further differentiated by the method used to create TSVs: either via-first or via-last. In the via-last approach, interconnect is created after wafers are bonded, whereas via-first processes build the TSVs on each wafer prior to the bonding process, which is generally more efficient and cost-effective [16]. SOI wafers have several advantages for 3D wafer stacking. Each wafer can be easily thinned to the buried oxide layer (BOX) since the buried layer is used as an etch stop for the silicon etch to produce a uniformly thin active layer.

#### 1.5 Tezzaron's 3D solution

Tezzaron 3D IC fabrication process approach, involved in the fabrication of the prototype chip subject of this thesis work, is wafer-level, via-first, with metalto-metal thermal bonding. This kind of bonding, realized by means of copper, provides both mechanical and electrical connectivity in one step. Copper bonding has the main benefit, with respect to other materials, of being already used as standard part of normal CMOS processing. Moreover, it provides excellent electrical and thermal dissipation characteristics and it is easily planarized using existing chemical mechanical polishing (CMP) technologies. Tezzaron has developed two kind of vertical interconnection between the layers, whose main characteristic are summarized in Table 1.1. The first generation of Tezzaron's interconnect, namely SuperVia, has the advantage of not requiring any foundry process changes, as the vertical interconnect is entirely post processed. However, each SuperVia requires an open field area with no transistors and no interconnect. The SuperVias diameter has also to be quite large in order to keep a conservative aspect ratio, constraining the density of the interconnect. On the other hand, the second generation of Tezzaron's interconnect, namely SuperContact, is built during wafer fabrication, so it requires the foundry to

|                       | $Super-Via^{TM}$ | $Super-Contact^{TM}$ |

|-----------------------|------------------|----------------------|

| Size [µm x µm x µm]   | 4.0 x 4.0        | 1.2 X 1.2            |

| Material              | Copper           | Tungsten             |

| Minimum pitch [µm]    | 6.08             | < 4                  |

| Feedthrough           |                  |                      |

| capacitance [fF]      | 7                | 2 - 3                |

| Series                |                  |                      |

| resistance $[\Omega]$ | < 0.25           | < 0.6                |

Table 1.1: Tezzaron's interconnect properties. [17].

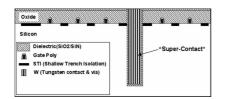

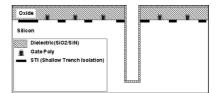

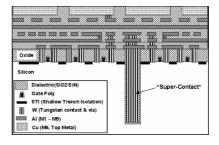

perform a unique process step. Pushing the vertical interconnect fabrication into the foundry significantly reduces the process complexity and equipment requirements for the subsequent stacking operation. The following sequence, Figs. 1.10-1.18, illustrates Tezzarons stacking method with the SuperContact interconnect.

Fig. 1.10 shows the cross-section of one wafer, immediately after transistors have been created, but before contact metal. In Fig. 1.11 the vertical Super-Contact is etched through the oxide and into the silicon substrate approximately 6  $\mu m$ ; the walls are lined with silicon oxide or silicon nitride. The SuperContact is filled with tungsten and finished with CMP polishing, as shown in Fig. 1.12. This operation completes the unique processing requirements at the wafer level. The wafer is finished with its normal processing, as shown in Fig. 1.13, which can include a combination of aluminum and copper wiring layers. It is worth noticing that the last layer must be copper. All the wafers included in the 3D stack are processed by means of the discussed process. Then, the first and the second wafer are aligned and bonded in a copper thermal diffusion process that takes places in a vacuum at approximately  $375^{\circ}$  and 40 psi. The step is shown in Fig. 1.14. Several minutes are required to form the bond: typical cycle time within the bonder is 20 minutes. After bonding, the top wafer is thinned to the bottom of the SuperContact, as shown in Fig. 1.15. This leaves a substrate thickness of about 6  $\mu$ m. Thinning is done with a combination of wafer grinding, CMP and etching. The backside of the thinned wafer is covered by an oxide, then a single damascene copper process creates bonding pads for subsequent stacking. In Fig. 1.16 a third wafer has been added to the stack, using the same technique by which the second wafer was added. Then, the stack is inverted, as shown in Fig. 1.17: indeed final processing will be applied to the backside of the first wafer. The first wafer

undergoes the same thinning process used before, stopping on the tungsten SuperContact, as shown in Fig. 1.18. Instead of a copper damascene process for bonding pads, an aluminum layer is deposited for normal wire bonding.

Figure 1.10: Cross-sectional view of the wafer.

Figure 1.12: SuperContact is filled with tungsten.

Figure 1.11: SuperContact creation.

Figure 1.13: The first wafer is finished with its normal processing.

Figure 1.14: Interconnection of the two wafers

Figure 1.15: Fabrication of the bonding pads for subsequent stacking

Figure 1.16: A third wafer is added to the stack.

Figure 1.17: The stack is inverted.

Figure 1.18: Aluminum layer is deposited for wire bonding.

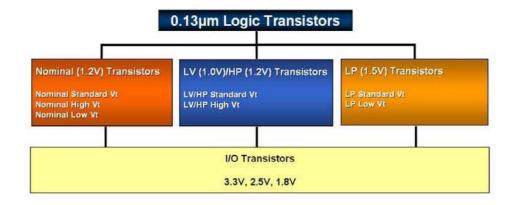

Tezzaron has stacked a variety of wafer types, including SOI and bulk wafers, using both the original Super-Via and the new enhanced second generation process flows. Experiments have shown that the 3D-enabled wafers can be thinned to as little as a few microns. They can be stacked with sub-micron alignment. The bonded wafers have a Cu-Cu bond strength that is greater than required and actually stronger than the Cu-SiO<sub>2</sub> interface. Also, the interconnected wafers can be handled in a normal fashion without special handlers or precautions. The transistors on the stacked, bonded, and thinned wafers were shown to have no discernable performance differences from their original 2D form. Tezzaron Semiconductor has chosen the Chartered Semiconductor 0.13  $\mu m$  process as the candidate process in the fabrication of their 3D devices. Chartered's 0.13 µm process offerings includes logic, high performance, low voltage and low power. Chartered's logic process is built upon a modular architecture that allows modules of embedded memory, analog/mixed signal and RF CMOS to be easily and efficiently incorporated. With up to eight metal layers available, Chartered's 0.13 µm solutions offer a variety of transistor options with multiple threshold voltages, including 1.0, 1.2 and 1.5V core, and 2.5 and 3.3V I/O, making them well-suited for a large variety of applications. Chartered's 0.13 µm process offers deep N-well (DNW) structure which can be incorporated for noise isolation from adjacent switching circuits or for other special functions, as in the case of DNW-MAPS discussed in the third chapter. The variety of transistors (see Fig. 1.19) can be used simultaneously in a design and are designed for compatibility with other industry processes,

Figure 1.19: Chartered 0.13  $\mu$ m process transistors.

allowing migration to other fabs. Chartered has an extensive silicon proven library for the 0.13  $\mu$ m process which includes standard cells, memory compilers and I/O cells. The 0.13  $\mu$ m process is currently available for 8-inch wafer production.

#### 1.6 MITLL's 3D solution

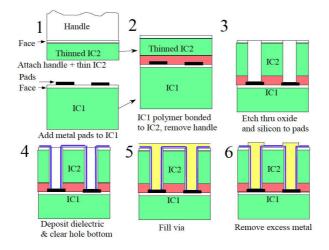

Another 3D integration scheme, developed recently at MITs Lincoln Laboratory, can interconnect three separate layers of circuitry on fully fabricated SOI-based wafers. The method involves inverting and aligning one wafer over another using an infrared registration technique, and then forming a lowtemperature oxide bond. Handle silicon is removed from the top-facing side of the inverted wafer in a stripping process, utilizing the buried oxide layer of the SOI wafer as an etch stop. Concentric 3D vias are then etched through both the top tier and the oxide-bonded layer all the way to the bottom-tier circuitry, and tungsten interconnect is deposited in a damascene process. The steps are repeated to add a third chip and to expose the underside of the top layer to serve as a bond pad in the final package. This process flow is schematically shown in Fig. 1.20. Proof-of-concept applications of Lincoln Labs three-tier integration approach include a ring oscillator test circuit, a 1024 x 1024 pixel imager with some one million 3D vias across the array, a photodiode laser radar and the bonding of a SOI CMOS circuit layer to an InP handle wafer, to enable higher-density and longer-wavelength focal plane detectors. Other

#### 1) Fabricate individual tiers **Buried Oxide** Handle Silicon Wafer-2 335 53 **Buried Oxide** Handle Silicon Wafer-1 2) Invert, align, and bond wafer 2 to wafer 1 nooiliS elbneH Vafer-2 عرك يرك Oxide كالدح العالات bond Wafer-1 3) Remove handle silicon from wafer 2, etch 3D Vias, deposit and CMP tungsten 3D Via Wafer-1 Handle Silicon 4) Invert, align and bond wafer 3 to wafer 2/1 assembly, remove wafer 3 handle wafer, form 3D vias from tier 2 to tier 3 1 4 5 Tier-Wafer-1 Handle Silicon

Figure 1.20: 3D SOI process flow.

3D concepts being explored by Lincoln Lab in conjunction with some industry and university partners include 3D FPGAs, ASICs, flash memory, and nano-radio and RF tags.

#### 24 CHAPTER 1. THREE DIMENSIONAL INTEGRATED CIRCUITS

# Chapter 2

# Characterization of a 180 nm CMOS SOI Technology

Silicon-on-insulator (SOI) is emerging as a strong technology candidate for low-power, high-performance applications [18]. Integrated circuits fabricated on SOI substrates have been of increasing interest as the starting material has improved in quality, leading to highly promising circuit results. Moreover, as earlier discussed, SOI technology is particularly well-suited for 3D design. Since the substrate is not electrically connected to the SOI transistors, it can be removed through etching: the buried oxide layer (BOX) provides an adequate etch stop. In MIT-LL's 3D SOI process, based on their 0.18  $\mu$ m technology, signals from adjacent levels in the stack can be interconnected through compact 2.5  $\mu$ m wide interdie vias [19].

SOI technology can be combined with vertical integration techniques in order to realize 3D multilayer structures including sensors and mixed-signal readout electronics with high functional density [20]. Furthermore, CMOS SOI technologies have become very attractive for the design of advanced sensor and readout electronics for the future generation of high energy physics (HEP) experiments [21], [22]. SOI detectors wafers are formed by bonding together a top wafer with low resistivity and a bottom wafer with high resistivity, by means of a silicon oxide bond. After bonding, the top wafer is thinned to just a few microns using one of several different techniques. The low resistivity layer may host the readout electronics, whereas in the high resistivity one it is possible to integrate fully-depleted detector elements.

In view of employing this technology in the fabrication of 3D sensors for HEP and imaging applications, an accurate characterization of SOI devices is mandatory. In this chapter the SOI MOSFET will be introduced, followed by the study of static, signal and noise performance of fully depleted siliconon-insulator (FD-SOI) devices, provided by MIT Lincoln Laboratory.

#### 2.1 SOI MOSFETs

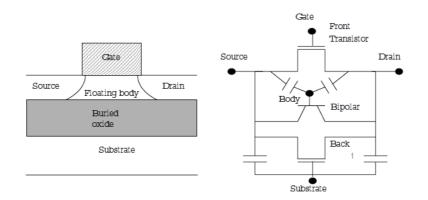

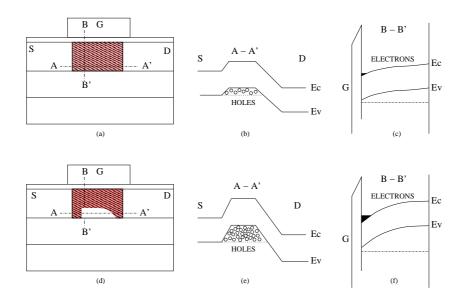

With silicon on insulator technology, MOSFETs are formed in a thin top silicon layer separated from the silicon substrate by an insulating layer. This structural feature provides SOI devices with several advantages for high-speed, low-power operation. Fig. 2.1 shows the SOI structure and its equivalent electrical representation. Depending on silicon thickness and body doping value, the channel region can be fully depleted (FD) or partially depleted (PD). The FD-SOI, in principle, are not affected by kink-effect or by other effects related to the floating body of the device. The key feature of a FD-SOI MOSFET is

Figure 2.1: SOI transistors.

represented by the fact that the depletion region reaches all the way to the bottom of the silicon film. As a result, the body region is fully depleted, as the name of the device indicates. Usually, for deep submicron technologies, optimization of FD devices requires an ultra-thin silicon layer while only a thin silicon layer (about 100 nm) is adopted in the case of PD devices. Fig. 2.2 (a) shows the cross-sectional structure of an FD-SOI nMOSFET; (b) is an energy band diagram along the line A-A' in (a), which runs through the source, body, and drain near the bottom of the body region; (c) is an energy band diagram showing how the energy bands change along the line B-B' in (a), which runs from the gate oxide film down into the body region near the

Figure 2.2: FD- and PD-SOI MOSFETs. (a) Cross section of an FD-SOI device, (b) the energy band diagram along the line A-A', and (c) the energy band diagram along the line B-B'. (d-f) show the corresponding figures for a PD-SOI device.

source end. The corresponding figures for a PD-SOI nMOSFET are shown in Fig. 2.2 (d-f). In a FD-SOI device, the entire body region is depleted in both the "on" and "off" states, as shown in Fig. 2.2 (a). In contrast to an FD-SOI device, a PD-SOI device has an undepleted neutral region at the bottom of the body region, as shown in (d). This difference results in a different potential distribution inside the body region. In an FD-SOI device, the entire body region has a potential gradient in the depth direction, as shown in (c), and the gate field extends right into the BOX. In a PD-SOI device, the influence of the gate field stops inside the body region, as shown in (f), and there is a neutral region with no potential gradient at the bottom of the body region. Accordingly, the potential difference between the top and the bottom of the body region is larger in PD device and the potential barrier to holes between the source and the body near the bottom of the body region is higher. This difference in the barrier height for holes leads to a difference in the number of holes that accumulate in the body region. Holes are generated by impact ionization near the drain. During the operation of an nMOSFET, when channel electrons pass through the high-electrical-field region near the drain, they

Figure 2.3: SOI and bulk CMOS inverters.

gain energy from the field and jump to higher energy levels. The high-energy electrons collide with valence electrons and generate more electrons and holes. The electrons flow into the drain, and the holes flow toward the source via the bottom of the body region. When this happens, more holes accumulate at the bottom of the body region in a PD-SOI than in an FD-SOI device because PD-SOI device has a higher potential barrier. This leads to a large difference between the floating-body effects of the two types of devices, such as the kink in the drain current-voltage characteristics and the stability of the dynamic characteristics.

Compared to a classical bulk transistor, SOI can reduce the capacitance at the source and drain junctions significantly by eliminating the depletion regions extending into the substrate. This results in a reduction in the RC delay due to parasitic capacitance, and hence a higher speed performance of the SOI CMOS devices compared to bulk CMOS. The independent body bias of SOI MOSFETs makes them faster in a stacked-gate structure: in the stacked gates made with bulk MOSFET the negative body bias increases the threshold voltage and lowers the operating speed. In contrast, the body bias of stacked SOI MOSFETs is positive because it takes a value between the source and drain voltage. This yields a lower threshold voltage for stacked transistors, thereby enhancing the operating speed. Moreover, SOI devices are laterally isolated from each other by an insulator film, and vertically isolated from the substrate by the BOX, which makes the isolation ideal. As a result, SOI devices can be packed closer together than bulk ones. In addition, the n+ and p+diffusion regions at the output of a CMOS inverter can be connected directly to each other, as shown in Fig. 2.3, which makes the area of the device smaller than that of a bulk one.

#### 2.2 Investigated devices

The static and noise analysis is carried out for both N-channel and P-channel FD devices with various gate geometries. The BOX thickness of the investigated devices is 400 nm and the thickness of the active silicon film above the BOX is 40 nm. The maximum allowed supply voltage  $V_{DD}$  is 1.5 V. For all devices a body contact pad, which was grounded during the measurements, is available. Gate dimensions of investigated devices (gate width W and gate length L) are shown in table 2.1. The same geometries are available for both N-channel and P-channel devices. The MOSFETs are mounted in a 40 pins DIL package; all device contacts have no protecting diodes. MOSFET featuring a W/L=8/0.2 were provided with a contact between body and source.

|      | $W \ [\mu m]$ | $L \ [\mu m]$ | Note |

|------|---------------|---------------|------|

| NMOS | 100           | 0.5           |      |

|      |               | 0.2           |      |

|      | 60            | 0.5           |      |

|      | 8             | 0.2           |      |

|      | 8             | 0.2           | S    |

| PMOS | 100           | 0.5           |      |

|      |               | 0.2           |      |

|      | 60            | 0.5           |      |

|      | 8             | 0.2           |      |

|      | 8             | 0.2           | S    |

Table 2.1: Gate geometries of the N-channel and P-channel devices. Devices marked with S are of body-tied-to-source (BTS) type.

#### 2.3 Static measurements

For each device the following measurements have been performed to study the static behavior:

- $I_D$  versus  $V_{GS}$  with  $V_{DS}$  as a parameter and  $V_{BS}=0$

- $I_D$  versus  $V_{DS}$  with  $V_{GS}$  as a parameter and  $V_{BS}=0$

The value of the transconductance  $g_m$ , defined as:

$$\frac{\partial I_D}{\partial V_{GS}} \tag{2.1}$$

was extracted from  $I_D$ - $V_{GS}$  curves. Measurements of static parameters were carried out by means of an Agilent E5270B Precision Measurement Mainframe with E5281B SMU Modules.

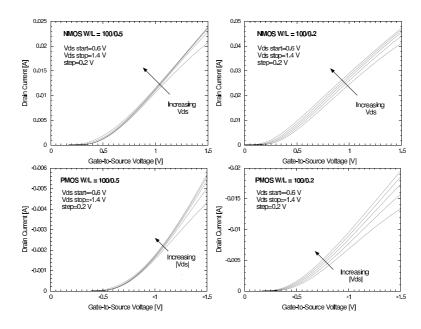

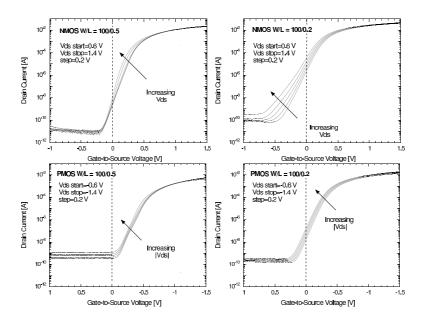

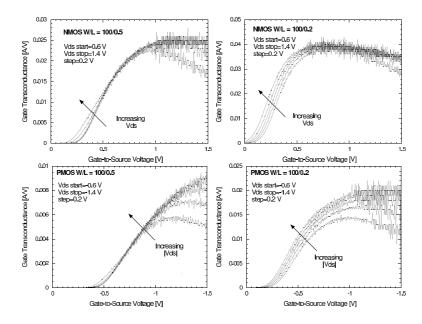

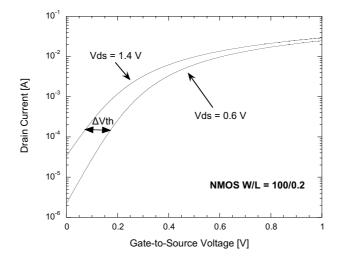

Fig. 2.4 shows the  $I_D$ - $V_{GS}$  characteristic for NMOS and PMOS devices featuring a gate width of 100 µm and gate lengths of 0.5 and 0.2 µm, for different values of the  $V_{DS}$  voltage, whereas Fig. 2.5 shows the same characteristics in a logarithmic scale. From these plots it is possible to notice a lateral shift in the curves, which points out that some devices are significantly affected by the drain induced barrier lowering: this effect will be discussed in section 2.5.

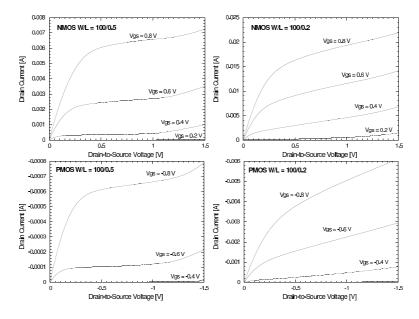

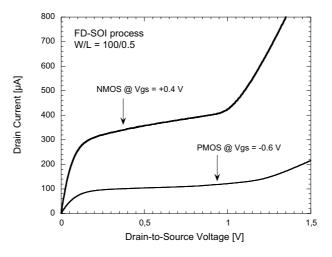

Fig. 2.6 shows the  $I_D$ - $V_{DS}$  characteristic for different values of the gate-tosource voltage. It is possible to notice that, for lower  $V_{GS}$ , NMOS devices are more significantly affected by the kink effect with respect to the PMOS devices.

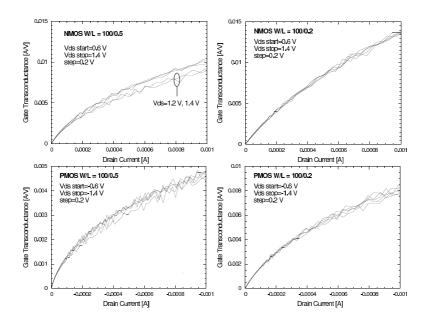

Figs. 2.7 and 2.8 show the gate transconductance as a function of the gate-tosource voltage and of the drain current respectively, for different values of the drain-to-source voltage.

30

**Figure 2.4:** Drain current  $I_D$  versus  $V_{GS}$  at different  $V_{DS}$ , for both N-channel and P-channel devices.

**Figure 2.5:** Drain current  $I_D$  (in logarithmic scale) versus  $V_{GS}$  at different  $V_{DS}$ , for both N-channel and P-channel devices.

**Figure 2.6:** Drain current  $I_D$  versus  $V_{DS}$  at different  $V_{GS}$ , for both N-channel and P-channel devices.

**Figure 2.7:** Gate transconductance  $g_m$  versus  $V_{GS}$  at different  $V_{DS}$ , for both N-channel and P-channel devices.

**Figure 2.8:** Gate transconductance  $g_m$  versus  $I_D$  at different  $V_{DS}$ , for both N-channel and P-channel devices.

## 2.4 Noise measurements

The spectral density of the noise in the channel current of the examined devices was studied by measuring the equivalent noise voltage spectrum referred to the gate. These measurements were carried out with a Network/Spectrum Analyzer HP4195A and a purposely developed interface circuit which allows for noise measurements in the frequency range 100 Hz-100 MHz [23]. Noise measurements have been performed in the low current density region which is of major concern for low-power applications. In particular, the devices were characterized at  $V_{DS}=0.6$ , 0.8, 1.0, 1.2, 1.4 V and at  $I_D=0.050$ , 0.10, 0.25, 0.50, 1.00 mA; body terminal was kept to ground for all noise measurements. A large set of noise measurements is focused on device behavior under different drain-to-source voltages in order to evaluate the effect of this bias condition on the low-frequency noise.

A subset of the results of the performed measurements, with some of relevant comparison between spectra, is presented in this section.

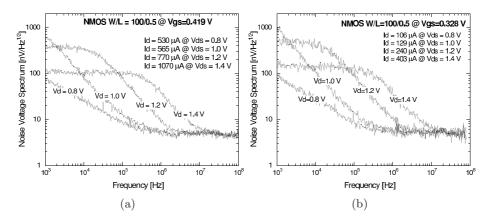

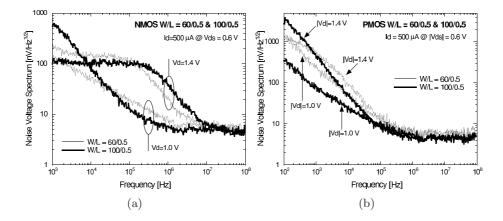

Fig. 2.9 show the noise voltage spectra of an NMOS device featuring a W/L=100/0.5 for different drain-to-source voltages and for different drain currents. It is possible to notice that the noise spectrum exhibits a lorentzian-like contribution as  $V_{DS}$  increases. The same behavior is shown in Fig. 2.10 (a), which displays the noise voltage spectra of two NMOS featuring a gate length of 0.5 µm and with different gate width. The same plot is shown in Fig. 2.10 (b) for PMOS devices.

Figure 2.9: Noise voltage spectra of an NMOS with W/L=100/0.5 at different drain-to-source voltage.  $I_D=500 \ \mu\text{A}$  (a),  $I_D=100 \ \mu\text{A}$  (b) @  $V_{DS}=0.6 \ \text{V}$ .

Figure 2.10: Noise voltage spectra of two NMOS (a) and two PMOS (b) with  $L=0.5 \ \mu\text{m}$  and variable W at different drain-to-source voltage  $(I_D=500 \ \mu\text{A} @ V_{DS}=0.6 \text{ V}).$

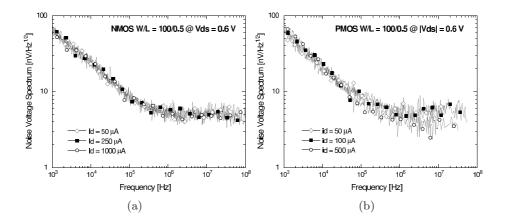

Fig. 2.11 displays the noise voltage spectra for devices of both polarity for different drain currents. It is possible to notice, in the case of NMOS devices, that high frequency noise contribution is almost independent of the drain current. This may be due to parasitic resistances associated with the device, as discussed in section 2.6.

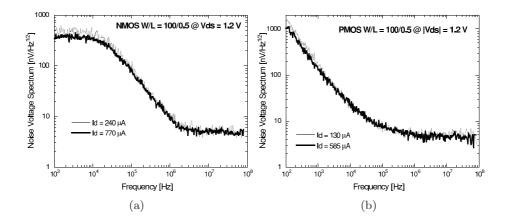

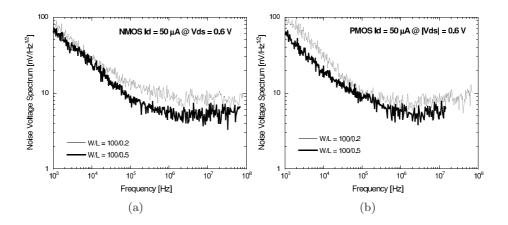

Fig. 2.12 shows the noise voltage spectra of NMOS and PMOS devices with W/L=100/0.5 for a drain-to-source voltage (absolute value) of 1.2 V and for two different values of the drain current, whereas plots in Fig. 2.13 display the noise voltage spectra of MOSFETs with a gate width of 100 µm varying the gate length. It is possible to notice that excess white noise, already highlighted in Fig. 2.11 (a), increases when the gate length is shrinked.

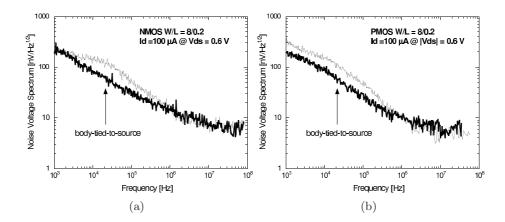

As a last comparison, Fig. 2.14 shows the noise voltage spectra of devices featuring a W/L=8/0.2 with and without body tied to source, for a drain current of 100  $\mu$ A. Body-tied-to-source devices exhibit a smaller low frequency noise contribution.

Figure 2.11: Noise voltage spectra of an NMOS (a) and a PMOS (b) with W/L=100/0.5 at  $|V_{DS}|=0.6$  V for different drain current.

Figure 2.12: Noise voltage spectra of an NMOS (a) and a PMOS (b) with W/L=100/0.5 at  $|V_{DS}|=1.2$  V for two different bias conditions.

**Figure 2.13:** Noise voltage spectra of two NMOS (a) and PMOS (b) with  $W=100 \ \mu\text{m}$  and different  $L \ (I_D=50 \ \mu\text{A} \ @ V_{DS}=0.6 \ \text{V}).$

Figure 2.14: Noise voltage spectra of two NMOS (a) and PMOS (b) with W/L=8/0.2 with and without body tied to source, for a drain current of 100  $\mu$ A.

## 2.5 Analysis of static measurement results

Two interesting features related to SOI devices behavior have been highlighted by the static measurements: kink effect and drain induced barrier lowering (DIBL). It is well-know that SOI nMOSFETs exhibit floating body effect [24], which may result in typical kinks in the drain current  $I_D$  versus drain-to-source voltage  $V_{DS}$  characteristics. The kink effect is due to impact ionization arising from channel current carriers accelerated in the high-field depletion region, where they create electron-hole pairs.

The generated holes may accumulate in the device body, increasing its po-

Figure 2.15: Drain current as a function of the drain-to-source voltage for FD-SOI MOSFETs with W/L = 100/0.5.

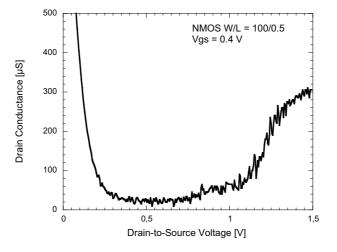

tential and decreasing the threshold voltage, as discussed in section 2.1. As a result,  $I_D$  shows a steep increase when  $V_{DS}$  exceeds a value needed for a significant impact ionization to occur. As shown in Fig. 2.15, the FD-SOI NMOS transistors clearly exhibit a kink effect in the  $I_D$ - $V_{DS}$  characteristic, which points out that they do not operate in an ideal full depletion mode. In order to reduce the kink effect, a method is to provide an effective body contact for the device, but this will increase the area of the circuit losing the feature of high device density and small parasitic capacitance. For the investigated devices, the presence of a single body contact does not appear to be effective in suppressing these effects. This can be explained by the high resistance of the thin body region [25]. As expected, kink effect is less evident in pMOSFETs, since holes are less effective than electrons in giving impact ionization. Kink effects worsen the differential drain conductance of the device as shown in Fig. 2.16 and affect the performance of analog circuits. For an amplifier, the gain at low frequency is substantially degraded with the kink effect.

Drain conductance can be affected also by the drain-induced barrier low-

Figure 2.16: Drain conductance as a function of the drain-to-source voltage for a FD-SOI nMOSFETs with W/L = 100/0.5.

ering (DIBL), especially for short-channel devices operating at low levels of inversion. DIBL effects is represented by a decrease in the threshold voltage,  $V_T$ , while increasing the  $V_{DS}$ . As  $V_T$  decreases, the overdrive voltage  $V_{OV} = V_{GS} - V_T$  increases, increasing the drain current. This effect can be explained by either the barrier-lowering or charge-sharing concept [26]. In the barrier-lowering concept, decreasing the channel length places the drain and the source closer together resulting in a deeper depletion region under the channel. This depletion region is further deepened with increasing  $V_{DS}$  as the depletion region around the drain increases. This effect results in less substrate control, lower depletion capacitance, and increased silicon surface potential. Increasing  $V_{DS}$  then lowers the potential barrier, attracts more carriers to the channel and, correspondingly, increases the drain current. In the charge-sharing concept, channel operation is influenced by the source and the drain, in addition to the gate and the substrate. This is especially true for short-channel devices where the drain is close to the channel and acts as a secondary gate generating field lines terminating on the channel. Increasing  $V_{DS}$  then enhances the channel beyond its regular gate and substrate control and increases the drain current. Both the barrier-lowering and charge-sharing

concepts describe increasing channel enhancement and drain current with increasing  $V_{DS}$  for a fixed value of  $V_{GS}$ .

The DIBL effect becomes obvious when looking at the transfer curves of a MOS transistor biased at different  $V_{DS}$ , in a semi-logarithmic plot as in Fig. 2.5 pointing out that investigated NMOS devices with small gate length are significantly affected by DIBL.

Without DIBL the curves would coincide in the subthreshold regime, otherwise a shift between curves can be observed in that operating region. With reference to Fig. 2.17, the DIBL effect can be measured by the lateral shift of the transfer curves in the subthreshold regime divided by the drain voltage difference of the two curves:

$$DIBL = \frac{\Delta V_T}{\Delta V_{DS}} \tag{2.2}$$

For the considered device, a NMOS with W/L=100/0.2, DIBL turns out to

Figure 2.17: Drain current as a function of the drain-to-source voltage for FD-SOI MOSFETs with W/L = 100/0.5.

be about -125 mv/V. DIBL effects significantly increase the drain conductance  $g_{ds}$ : the change in drain current  $\Delta I_D$ , resulting from a change in  $V_T$ ,  $\Delta V_T$ , due to DIBL is given by:

$$\Delta I_D = g_m(-\Delta V_T); \tag{2.3}$$

$V_T$  acts as a negative, small-signal, gate to source voltage since its increase lowers the drain current. Dividing Equation (2.3) by  $\Delta V_{DS}$  that causes  $\Delta V_T$  and  $\Delta I_D$  gives:

$$g_{ds} = \frac{\Delta I_D}{\Delta V_{DS}} = \frac{g_m(-\Delta V_T)}{\Delta V_{DS}} \tag{2.4}$$

where  $\Delta V_T / \Delta V_{DS}$  is the DIBL term which expresses the change in the threshold voltage with respect to  $V_{DS}$ . Since this term is negative,  $g_{ds}$  due to DIBL is positive, consistent with the increase in drain current caused by increasing  $V_{DS}$ .

## 2.6 Analysis of noise measurement results

In a MOSFET, the noise in the channel current can be expressed by an equivalent noise voltage source referred to the gate of the device. A rather general expression for the power spectral density of the voltage noise is:

$$S_V^2(f) = S_W^2 + S_{1/f}^2(f) + S_L^2(f).$$

(2.5)

#### 2.6.1 White noise

In (2.5), the first term is given by channel thermal noise, and by other thermal noise sources associated to device parasitic resistors, such as the source resistance  $R_{SS'}$ , the gate resistance  $R_{GG'}$  and the body resistance  $R_{BB'}$ . Therefore, the expression for the white noise spectral density can be approximated in the following way:

$$S_W^2 = 4k_B T \left[ \frac{\Gamma}{g_m} + R_{SS'} + R_{GG'} + R_{BB'} \frac{g_{mb}^2}{g_m^2} \right]$$

(2.6)

where  $\Gamma$  is a coefficient whose value depends on the inversion region where the device is operated,  $g_m$  is the gate transconductance and  $g_{mb}$  is the bulk transconductance. Equation (2.6) can be also written as follows:

$$S_W^2 = 4k_B T \frac{\Gamma}{g_m} + 4k_B T R_{par} \tag{2.7}$$

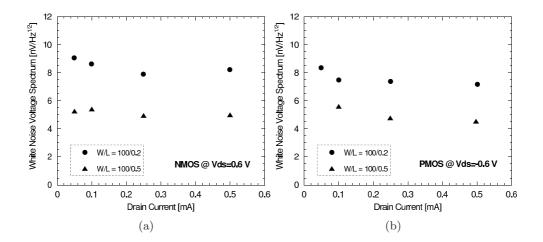

where the first term in (2.7) is given by channel thermal noise while  $R_{par}$ includes all contributions from parasitic resistors. In the low current density operating region the contribution from parasitic resistors usually has a minor impact. Therefore, according to equations (2.6) and (2.7), the white component of the noise voltage spectrum decreases with the increase of the drain current since the transconductance correspondingly increases. Fig. 2.18 shows the measured values of white noise voltage spectrum as a function of the

Figure 2.18: White noise voltage spectrum as a function of the drain current  $I_D$  for N-channel (a) and P-channel (b) devices with  $W=100 \ \mu m (|V_{DS}|=0.6 \ V)$ .

drain current for N-channel and P-channel devices. From these plots a sizable contribution from  $R_{par}$  is noticed. In particular, parasitic body resistor  $R_{BB'}$  generates drain current fluctuations through the body transconductance  $g_{mb}$ . Since the ratio  $g_{mb}/g_m$  is independent of the drain current [26], as shown in Fig. 2.19, this contribution is not expected to change at different  $I_D$  and results to be the dominant term in white noise in the  $I_D$  range investigated in the performed measurements, as shown in Fig. 2.11 (a).

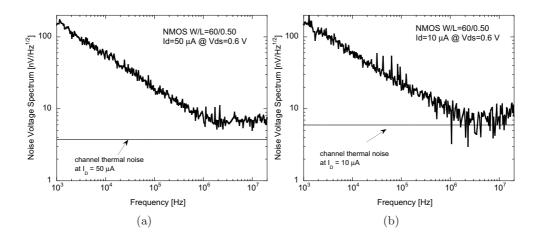

This excess noise term increases as the gate length decreases, as shown in Fig. 2.13 (a), because  $R_{BB'}$  also increases. For channel thermal noise to be dominant with respect to the  $R_{BB'}$  contribution, the device has to be operated at very low current density. At smaller drain current, indeed,  $g_m$  decreases and channel thermal noise gives a larger contribution to the total white noise voltage spectrum. Fig. 2.20 shows the noise voltage spectra of an FD-SOI NMOS measured at  $I_D = 50 \ \mu\text{A}$  and  $I_D = 10 \ \mu\text{A}$ , together with the channel thermal noise values calculated according to the first term in (2.6) and to  $g_m$  values measured at the same drain current.

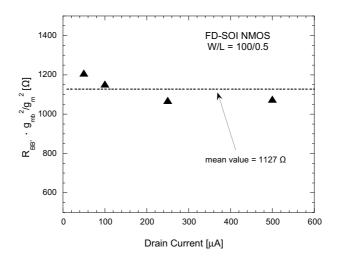

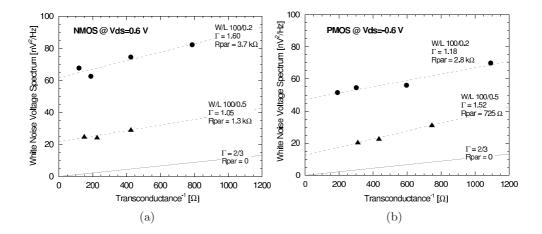

According to equation (2.7), plotting the measured values of white noise voltage spectrum as a function of  $1/g_m$  it is possible to extract the experimental values of  $\Gamma$  and  $R_{par}$  from the resulting straight line as shown in Fig. 2.21. In the same plots theoretical values of  $S_W^2$  obtained with  $\Gamma=2/3$  and  $R_{par}=0$ are also shown. The experimental values extracted for these parameters are

Figure 2.19:  $R_{BB'}g_{mb}^2/g_m^2$  as a function of the drain current, for a NMOS with W/L = 100/0.5

Figure 2.20: Noise voltage spectra of an FD-SOI NMOSFET with W/L = 60/0.5 at  $I_D = 50 \ \mu\text{A}$  (a) and  $I_D = 10 \ \mu\text{A}$  (b), and channel thermal noise value calculated at the same drain current.

summarized in Table 2.2. From these data, it is possible to notice how the parasitic resistance  $R_{BB'}$  increases as the gate length decreases, accordingly with the behavior highlighted in Fig. 2.13.

Figure 2.21: White noise voltage spectrum as a function of  $1/g_m$  for N-channel (a) and P-channel (b) devices with  $W=100 \ \mu m \ (V_{DS}=0.6 \ V)$ .

| Polarity | $L \ [\mu m]$ | Γ                 | $R_{par} \left[ \Omega \right]$ |

|----------|---------------|-------------------|---------------------------------|

| NMOS     | 0.2           | $1.60 {\pm} 0.40$ | $3700 \pm 200$                  |

|          | 0.5           | $1.05 {\pm} 0.40$ | $1300{\pm}100$                  |

| PMOS     | 0.2           | $1.18 {\pm} 0.20$ | $2800{\pm}100$                  |

|          | 0.5           | $1.52{\pm}0.10$   | $725\pm70$                      |

**Table 2.2:** White noise parameters  $\Gamma$  and  $R_{par}$ .

## 2.6.2 1/f noise

The second term in (2.5) describes the 1/f noise in the channel current. In weak inversion and in saturation, the following relationship can be used to model this noise contribution:

$$S_{1/f}^2(f) = \frac{K_F}{C_{OX}WL} \frac{1}{f^{\alpha_F}}$$

$$(2.8)$$

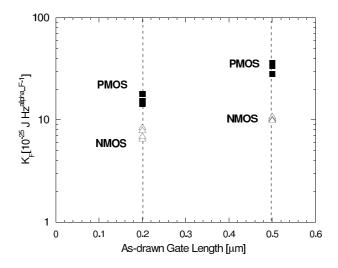

where  $K_F$  is an intrinsic process parameter for 1/f noise,  $C_{OX}$  is the gate oxide capacitance per unit area whose value is about 8.8 fF/µm<sup>2</sup> for 4 nm of corresponding electrical gate oxide thickness. The exponent  $\alpha_F$  determines the slope of this low frequency noise term. Values of coefficients  $K_F$  and  $\alpha_F$  have been extracted for both N-channel and P-channel devices at  $|V_{DS}|=0.6$  V and at different drain current values. Coefficient  $\alpha_F$  does not exhibit any clear dependence on the drain current while a slight variation with the channel length is observed. Due to the small set of investigated devices it is not possible to establish a clear relationship between  $\alpha_F$  and L.

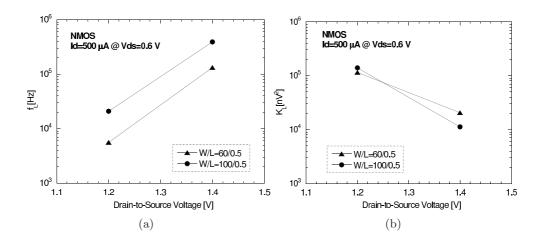

As shown in Fig. 2.22 coefficient  $K_F$  is variable with channel length while

**Figure 2.22:** 1/f noise coefficient  $K_F$  as a function of the gate length L for N-channel and P-channel devices with  $W=100 \ \mu m (|V_{DS}|=0.6 \ V)$ .

it does not exhibit any clear dependence on the drain current. Typical values of 1/f noise coefficients obtained for devices of both polarities are reported in Table 2.3.  $K_F$  values have been extracted by using the mean value of  $\alpha_F$ shown in the table. For comparison purposes, the table reports data relevant to devices in a 0.18 µm bulk CMOS process from different foundries [27]. According to Table 2.3,  $K_F$  and  $\alpha_F$  values for SOI NMOSFETs are very close to those featured by bulk NMOS devices. For SOI PMOSFETs,  $K_F$  coefficient is instead larger than for bulk counterparts, highlighting the worse 1/f noise properties of the examined process for this device polarity. In bulk CMOS, the fact that PMOSFETs feature a smaller low-frequency noise than equally sized NMOSFETs was generally related to buried channel conduction [28], In SOI CMOS, the active silicon film is so thin that the conduction takes place close to the surface and to oxide traps also in P-type devices. This might be the reason why the magnitude of their 1/f noise is higher than the bulk counterparts.

| Foundry | Polarity | $\alpha_F$ | $K_F \ [10^{-25} \mathrm{JHz}^{\alpha_F - 1}]$ |

|---------|----------|------------|------------------------------------------------|

| MITLL   | NMOS     | 0.9        | 10                                             |

|         | PMOS     | 1.0        | 15                                             |

| TSMC    | NMOS     | 0.9        | 10                                             |

|         | PMOS     | 1.0        | 5                                              |

| STM     | NMOS     | 0.9        | 15                                             |

|         | PMOS     | 1.1        | 8                                              |

**Table 2.3:** 1/f noise coefficients  $K_F$  and  $\alpha_F$  from the investigated technology and from devices belonging to bulk CMOS processes in the 0.18 µm node.

#### 2.6.3 Lorentzian-like noise

At low frequency, in devices biased with  $V_{DS}>0.8$  V for the investigated frequency range, the noise voltage spectrum is observed to deviate from the  $1/f^{\alpha_F}$ behavior, showing a much higher slope and sometimes exhibiting a plateau. This can be due to the existence of kink-related lorentzian-like noise overshoot superimposed on 1/f noise. The noise overshoot spectrum can be expressed as:

$$S_L^2(f) = \frac{K_L(V_{DS})}{1 + [f/f_L(V_{DS})]^2}$$

(2.9)

where  $f_L$  is the corner frequency and  $K_L$  is the noise level of the plateau. It is important to note that the corner frequency is a function of  $V_{DS}$ , which shift toward higher frequencies as  $V_{DS}$  increases, while the noise level plateau decreases as  $V_{DS}$  increases. Values of these coefficients as a function of  $V_{DS}$ are shown in Fig. 2.23. The same values are summarized in Table 2.4.

| $W \ [\mu m]$ | $L \ [\mu m]$ | $V_{DS}$ [V] | $K_L [\mathrm{nV}^2]$ | $f_L$ [kHz] |

|---------------|---------------|--------------|-----------------------|-------------|

| 60            | 0.5           | 1.2          | $1.3 \cdot 10^5$      | 5.6         |

|               |               | 1.4          | $2.0 \cdot 10^4$      | 130         |

| 100           | 0.5           | 1.2          | $1.4 \cdot 10^5$      | 21          |

|               |               | 1.4          | $1.1 \cdot 10^4$      | 390         |

**Table 2.4:** Lorentzian-like noise coefficient  $K_L$  and  $f_L$  for N-channel devices.

**Figure 2.23:** Lorentzian-like noise coefficients  $f_L$  (a) and  $K_L$  (b) as a function of the drain-to-source voltage for N-channel devices.

## 2.7 Conclusions

This chapter presented the static, signal and noise characterization carried out on devices from a 180 nm FD-SOI CMOS process provided by MIT Lincoln Laboratory. The results point out that SOI MOSFETs noise performance is very close to that featured by bulk devices, especially for low drain currents that is the operating region of major concern for low power applications. A prototype 3D chip designed by Fermilab group involving the investigated SOI technology is the so called VIP chip [20], a three-layer, 20 µm-pitch pixel proposed for ILC applications. The tested chip exhibited some problems, such as trapped charge between layers during the fabrication, causing shift in transistor voltage thresholds. Moreover, the tests carried out on the VIP chip also point out that precision circuits such as current mirrors are hard to be designed in SOI due to possible trapped charge effects and local heating. To avoid difficulties in using a non commercial foundry such as MIT Lincoln Laboratory, our interest has shifted toward looking for commercial vendors for 3D, as Tezzaron Semiconductor, which fabricates wafers in a well established, high yield process.

## Chapter 3

# The sparsified data readout (SDR1) chip

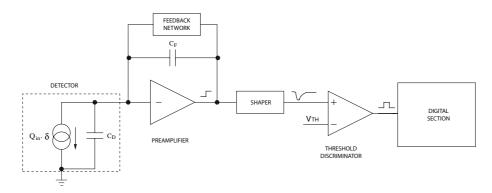

As discussed in the introduction, monolithic Active Pixel Sensors (MAPS) designed in a standard VLSI CMOS technology have recently been proposed as a compact pixel detector for the detection of charged particle in vertex/tracking applications. MAPS are already extensively used in visible light applications: with respect to other competing imaging technologies, MAPS sensors have several potential advantages in terms of low cost, low power, lower noise at higher speed, random access of pixels which allows windowing of regions of interest, ability to integrate several functions on the same chip.

This chapter discusses the properties of MAPS detectors involving a deep nwell (DNW) structure as the collecting element, and describes the main design features of the SDR1 (Sparsified Digital Readout) chip, which represents the first generation of vertically integrated MAPS with advanced readout architecture for high data rate. In particular, SDR1 is a general purpose prototype of a 3D device, being suitable for diverse applications such as imaging and particle tracking. However, its digital readout architecture was especially designed for vertexing applications to the International Linear Collider (ILC) facility: thus, in order to better understand the operating principles of the chip, the first section will be devoted to discuss the ILC specifications. The second section will introduce the general features of DNW monolithic active pixel sensors. The subsequent sections review the design criteria of the SDR1 chip and presents and discusses the operation and the expected performance of the sensor and the readout electronics. Finally, a set of results of analog and digital simulations, relevant to the analog front-end, the digital front-end and the digital back-end, will be presented.

## 3.1 Specifications for ILC

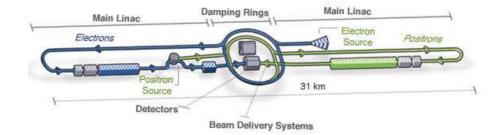

Figure 3.1: Schematic representation of the International Linear Collider

The International Linear Collider is one of the particle accelerators that is being proposed for the investigation of fundamental physics laws [29].

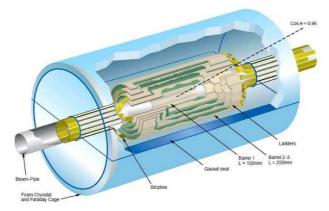

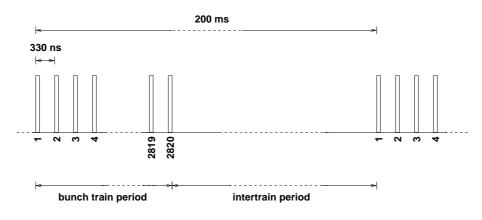

The ILC will accelerate elementary particles (electrons and positrons) along a straight path in beams focussed to a few nm in height and a few hundreds of nm in width and it is planned to have a collision energy of 500 GeV. In order to reconstruct particles trajectories, vertex detector will consists of five concentric cylinders [30] enclosing the beam interaction point, as shown in Fig. 3.2. The radius and length for each of the layers are shown in table 3.1 and result in a total vertex detector area of about 170000 mm<sup>2</sup>.

For the design of the detector and the readout electronics, it is necessary to

**Figure 3.2:** Schematic view of the vertex detector at the International Linear Collider.

| Layer | Radius [mm] | Half-length [mm] |

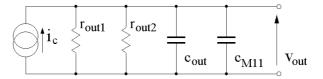

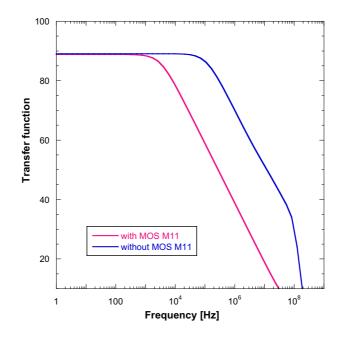

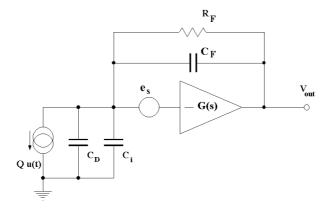

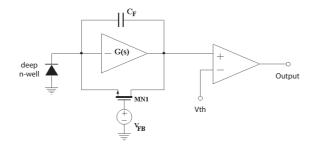

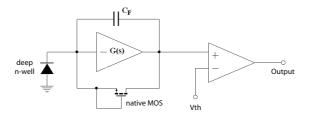

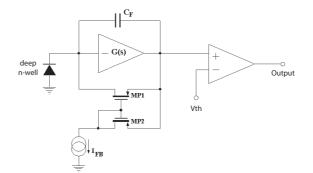

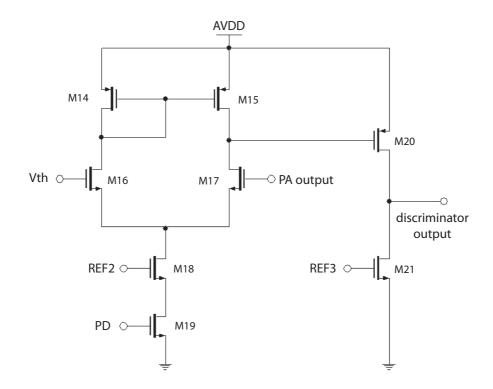

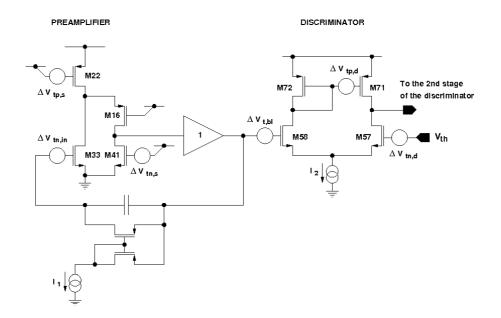

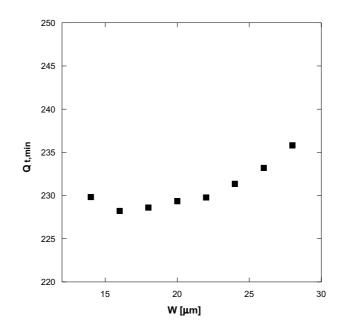

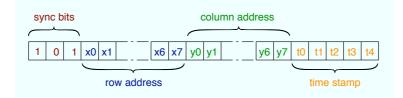

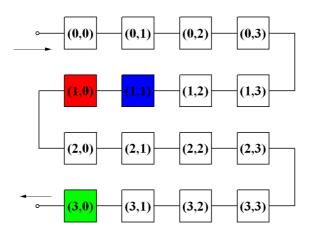

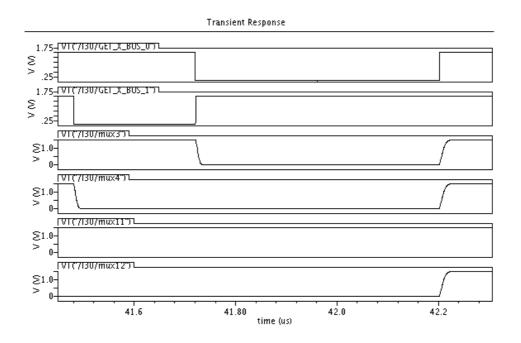

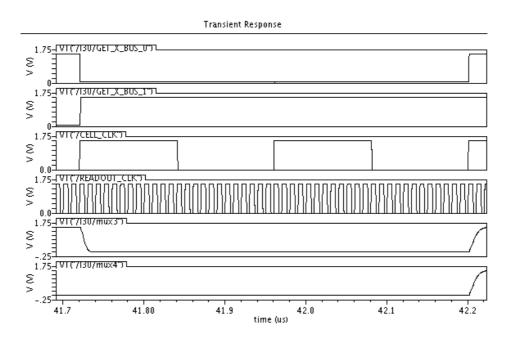

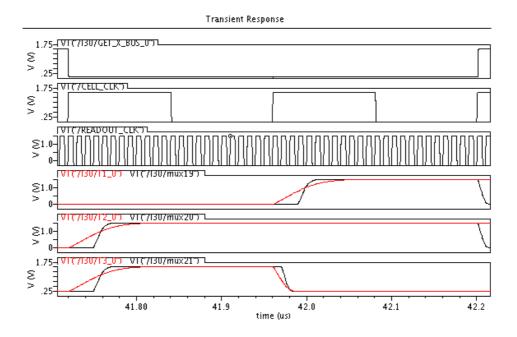

|-------|-------------|------------------|