# UNIVERSITY OF PAVIA - ITALY

DEPARTMENT OF ELECTRONIC ENGINEERING

Ph.D. Thesis in Microelectronics XXVI Cycle

## Adaptive Transmitters for Mobile Communications

Supervisor: Prof. Rinaldo CASTELLO Ph.D. Course Coordinator: Prof. Franco MALOBERTI

> Ph.D. Dissertation of Nicola CODEGA

${\it October}~2013$

### Introduction

The role of the back-end of a transceiver is to transmit a very large signal (compared to a received one), localized in a precise frequency range and it must not interfere with other communication channels, unrelated to the transmitted one, but surrounding it in the frequency domain. In fact, since the world is analog and not digital, it is not possible to make the signal power drop to zero beyond the defined channel, but some out-of-band emission will leak in other bandwidth channels. The risk is corrupting other signal's reception and recovery.

In particular, the risk is more higher for the receiver (RX) that is integrated on the same chip of the transmitter (TX) and is working in a Frequency Division Duplex (FDD) mode: the TX out-of-band leakage is directly coupled to the RX path through the duplexer attenuation, corrupting the received signal. Hence, this leakage must be very low, since the attenuation is not infinite.

In traditional implementations, the out-of-band emission was lowered through the use of an external, expensive and bulky SAW (Surface Acoustic Wave) Filter placed between the integrated transceiver and the external Power Amplifier that drives the duplexer before the antenna. However, during the years, reasearch efforts in TX design and CMOS technology improvements were able to eliminate the use of the SAW filter in the 2G, 2.5G and 3G standards.

The introduction of the LTE 4G standard has again raised the need to reuse the SAW filters to counteract the worsening of out-of-band performances due to the enlargement of the Radio Frequency (RF) signal bandwidths and, hence, the reduction of the frequency distances between the RX and the TX channel (RX-TX frequency offset). Besides the larger bandwidths, the power consumption necessary to process the signal has also become more demanding in 4G, being a crucial problem for devices that are supposed to run on battery. To solve the power consumption problem, we have to concentrate the efforts in the analog section of the transmitter, since it is the one that delivers the actual transmitted power to the antenna. Moreover, since out-of-band emission is intrinsically an analog issue, it's the analog section that must be optimized to lower this leakage. In this Thesis, the design of baseband sections for multistandard transmitters has been investigated.

In Chapter 1, a general overview of the new standard LTE is given, together with considerations about the out-of-band emission and contributors. An overview of recent multistandard transmitters from the State-of-the-Art closes the Chapter.

In Chapter 2, an improvement in terms of power consumption is given by a Class A/B approach in the active mixer of a transmitter working in voltage and current domain. The basic building blocks and design guidelines are described from a high-level point of view and the measurements of a realized prototype are discussed at the end of the Chapter.

In Chapter 3, a complete baseband working with a current approach from the DAC to the upconversion is described. The architecture and design of the main building blocks are highlighted. The last part of the Chapter is dedicated to the prototyping and measurements of the transmitter.

In Chapter 4, the benefits of pushing toward the theoretical limit the transmitter's building blocks is explained and demonstrated through simulations on two proposed "minimal" transmitters, oriented toward a 28nm and 55nm CMOS technology, working both entirely in Class A/B from the DAC to the upconversion.

## Contents

| Introduction ii |       |         | iii                                                                                            |           |

|-----------------|-------|---------|------------------------------------------------------------------------------------------------|-----------|

| Lis             | st of | Figure  | es                                                                                             | vii       |

| Lis             | st of | Tables  | 5                                                                                              | xi        |

| 1               | Stat  | e-of-tl | ne-Art of Transmitters for Mobile Communications                                               | 1         |

|                 | 1.1   | An int  | roduction to the Long-Term Evolution                                                           | 2         |

|                 |       | 1.1.1   | LTE Overview                                                                                   | 2         |

|                 | 1.2   | Out-of  | E-Band emission and modern transmitter parameters                                              | 5         |

|                 |       | 1.2.1   | General considerations $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 5         |

|                 |       | 1.2.2   | DAC Replicas                                                                                   | 7         |

|                 |       | 1.2.3   | Out-of-band noise                                                                              | 10        |

|                 |       | 1.2.4   | Non-linearities considerations: $ACLR$                                                         | 13        |

|                 |       | 1.2.5   | Error Vector Magnitude                                                                         | 15        |

|                 | 1.3   | State-o | of-the-Art Transmitters                                                                        | 17        |

|                 |       | 1.3.1   | Cassia [8]                                                                                     | 18        |

|                 |       | 1.3.2   | Giannini [9, 10]                                                                               | 19        |

|                 |       | 1.3.3   | Oliaei [12]                                                                                    | 21        |

|                 | 1.4   | Conclu  | isions                                                                                         | 23        |

| <b>2</b>        | An    | LTE T   | ransmitter using a Class $A/B$ Power Mixer                                                     | <b>25</b> |

|                 | 2.1   | Voltag  | e-mode Baseband                                                                                | 26        |

|                 |       | 2.1.1   | General Block Diagram                                                                          | 26        |

|                 |       | 2.1.2   | High-Order Filtering Block:                                                                    |           |

|                 |       |         | the Tow-Thomas Biquad $\ldots$                                                                 | 27        |

|                 |       | 2.1.3   | Operational Amplifier (OA) vs. Operational Transconduc-                                        |           |

|                 |       |         | tance Amplifier (OTA) $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$         | 29        |

|                 |       | 2.1.4   | Multipath OTA architecture                                                                     | 30        |

|                 |       | 2.1.5   | $5^{th}$ Order Filtering                                                                       | 32        |

|                 | 2.2   | Voltag  | e-to-Current (V-I) Converter and Active Upconverter $\ldots$ .                                 | 33        |

|                 |       | 2.2.1   | Conceptual Schematic                                                                           | 33        |

|                 |       | 2.2.2   | Class A vs. Class A/B Operation                                                                | 33        |

|                 |       | 2.2.3   | Class A/B OTA output stage                                                                     | 35        |

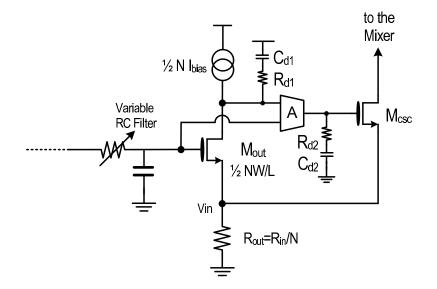

|                 |       | 2.2.4   | RC Filter inside the Current Mirror                                                            | 37        |

|                |                  | 2.2.5 Active Mixer $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 40 |

|----------------|------------------|-----------------------------------------------------------------------------------------------------|----|

|                | 2.3              | Prototype and Measurements                                                                          | 41 |

|                | 2.4              | Conclusions                                                                                         | 45 |

| 3              | A L              | ow Out-of-Band Noise LTE Transmitter with Current-Mode Approach                                     | 47 |

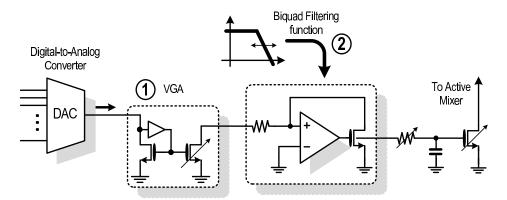

|                | 3.1              | Full Current-Mode Approach                                                                          | 48 |

|                |                  | 3.1.1 Introduction                                                                                  | 48 |

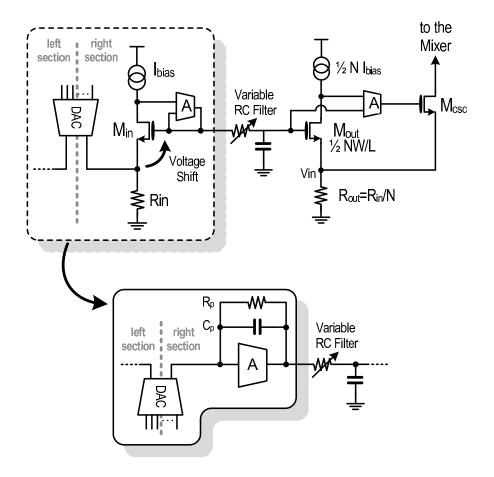

|                |                  | 3.1.2 Current-Mode Transmitter                                                                      | 49 |

|                | 3.2              | Current-Mode Transmitter: Building Blocks                                                           | 50 |

|                |                  | 3.2.1 Modifications to a Mixed-Mode Baseband                                                        | 50 |

|                |                  | 3.2.2 Variable Gain Amplifier                                                                       | 51 |

|                |                  | 3.2.3 Huijsing's Floating Battery [21] for a Class A/B VGA                                          | 52 |

|                |                  | 3.2.4 Current-Driven Biquadratic Cell                                                               | 54 |

|                | 3.3              | Prototype and Measurements                                                                          | 57 |

|                |                  | 3.3.1 $3^{rd}$ and $5^{th}$ order filtering configurations                                          | 57 |

|                |                  | 3.3.2 VGA for $3^{rd}$ order filtering configuration                                                | 58 |

|                |                  | 3.3.3 VGA for $5^{th}$ order filtering configuration                                                | 64 |

|                |                  | 3.3.4 Current-driven Biquad's Multipath OTA                                                         | 65 |

|                |                  | 3.3.5 OTA Common-Mode Feedbacks (CMFBs)                                                             | 66 |

|                |                  | 3.3.6 Power Consumptions                                                                            | 69 |

|                |                  | 3.3.7 Reconfigurability                                                                             | 70 |

|                |                  | 3.3.8 Measurements                                                                                  | 71 |

|                | 3.4              | Conclusions                                                                                         | 75 |

| 4              | Evo              | lution of a Multi-Standard Transmitter                                                              | 77 |

|                | 4.1              | Toward the Out-of-Band noise fundamental limit                                                      | 78 |

|                |                  | 4.1.1 Transmitter's fundamental blocks                                                              | 78 |

|                |                  | 4.1.2 Structure of the Baseband Transmitter                                                         | 79 |

|                |                  | 4.1.3 Considerations on the Architecture                                                            | 81 |

|                | 4.2              | Simulations of the proposed structure                                                               | 83 |

|                |                  | 4.2.1 Reconfigurability and frequency behaviour                                                     | 83 |

|                |                  | 4.2.2 Out-of-band Noise Performances                                                                | 86 |

|                | 4.3              | Transmitter Baseband with a $2^{nd}$ order passive filtering                                        | 87 |

|                |                  | 4.3.1 Considerations on the Architecture                                                            | 88 |

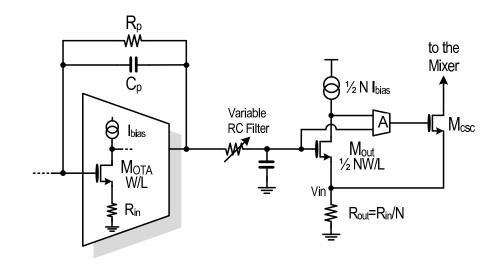

|                |                  | 4.3.2 Single-ended OTA for the damped integrator                                                    | 89 |

|                |                  | 4.3.3 Simulation results                                                                            | 92 |

|                | 4.4              | Conclusions                                                                                         | 98 |

| Conclusions 99 |                  |                                                                                                     |    |

| Bi             | Bibliography 101 |                                                                                                     |    |

|                |                  |                                                                                                     |    |

# List of Figures

| 1.1  | LTE20 signal spectrum, taken from a Spectrum Analyzer                                                    | 4  |

|------|----------------------------------------------------------------------------------------------------------|----|

| 1.2  | A typical block diagram of a transceiver.                                                                | 6  |

| 1.3  | A time-domain signal $x(t)$ and his Fourier Transform $X(f)$ in the                                      |    |

|      | frequency domain.                                                                                        | 7  |

| 1.4  | Signal $x(t)$ sampled in the time-domain and his spectrum                                                | 8  |

| 1.5  | Output signal of a real DAC and his spectrum                                                             | 9  |

| 1.6  | Numerical example of out-of-band noise requirement calculations for<br>a transmitter.                    | 10 |

| 1.7  | Out-of-band noise meaurements testbench.                                                                 | 11 |

| 1.7  | LTE20 signal spectrum (from a spectrum analyzer) used for out-of-                                        | 11 |

| 1.0  | band noise measurements and, below, transmitted signal spectrum                                          |    |

|      | through the RX-port of a duplexer                                                                        | 12 |

| 1.9  | Definitions of adjacent and alternate adjacent channels in a trans-                                      |    |

| 1.0  | mitted signal spectrum.                                                                                  | 14 |

| 1.10 | Qualitative linearity definition through a 4-tones simulation.                                           | 14 |

| 1.11 | $ACLR_{UTRA}$ and $ACLR_{E-UTRA}$ definitions on the transmitted sig-                                    |    |

|      | nal spectrum.                                                                                            | 15 |

| 1.12 | Signal constellation of a QPSK modulation: ideal (left) and dis-                                         |    |

|      | torted with $EVM$ (right) $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 17 |

| 1.13 | Baseband filtering in current-mode proposed by [8]                                                       | 18 |

| 1.14 | Baseband filtering in voltage-mode with a passive voltage mixer, pro-                                    |    |

|      | posed by $[9]$                                                                                           | 20 |

| 1.15 | Analog transmitter section diagram block proposed by $[12]$                                              | 22 |

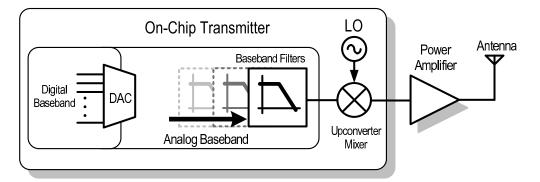

| 2.1  | Block schematic of the Multistandard Transmitter                                                         | 26 |

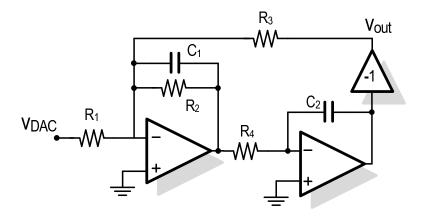

| 2.2  | Tow-Thomas Biquad schematic.                                                                             | 28 |

| 2.3  | On the left, a source follower used as output stage of an OA; on the                                     |    |

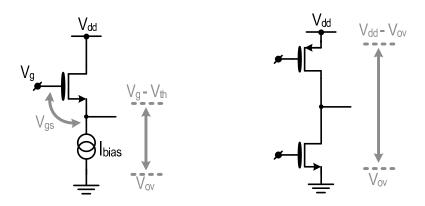

|      | right, an inverter as output stage of an OTA                                                             | 30 |

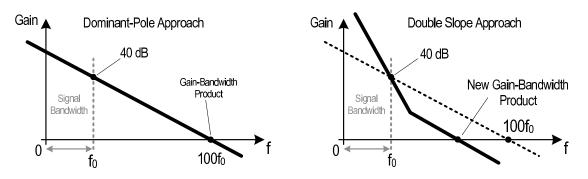

| 2.4  | Open-loop transfer function of an OTA with dominant pole approach                                        |    |

|      | (left) and with double-slope approach (right)                                                            | 31 |

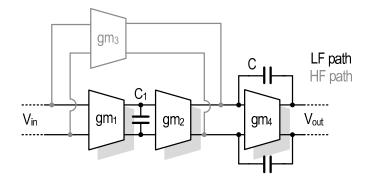

| 2.5  | Block diagram of a multipath OTA.                                                                        | 31 |

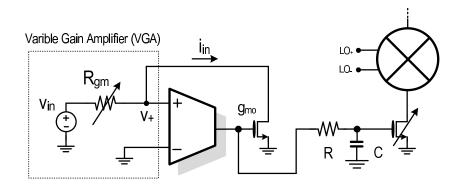

| 2.6  | Simplified schematic of the V-I converter driving the active mixer                                       | 33 |

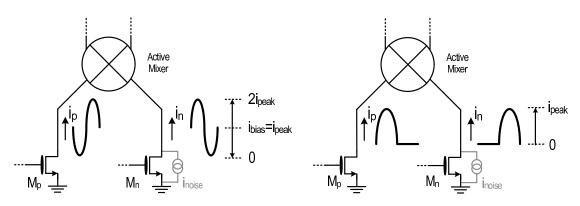

| 2.7  | Mixer transconductor working in Class A (left) and Class B (right).                                      | 34 |

| 2.8  | V-I converter OTA output stage in Class $A/B$ (the RC filtering has                                      |    |

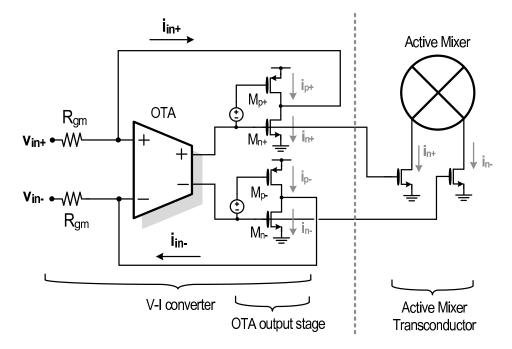

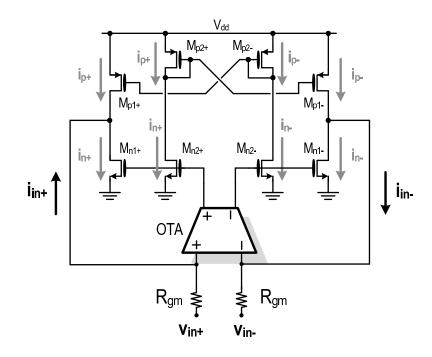

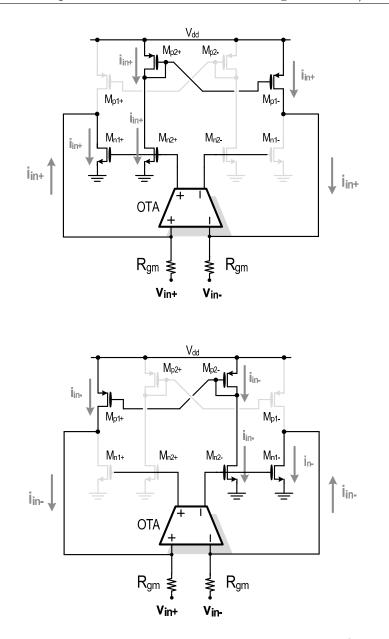

|      | been omitted) driving the active mixer.                                                                  | 36 |

| 2.9  | Proposed Class $A/B$ output stage of the V-I converter OTA                                               | 37 |

|      | $Current\ signal\ flowing\ in\ the\ unbalanced\ Class\ A/B\ output\ stage. \ .$                    | 38 |

|------|----------------------------------------------------------------------------------------------------|----|

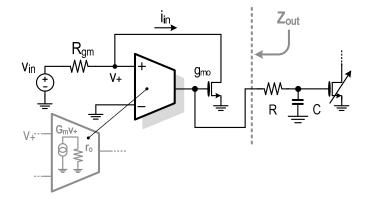

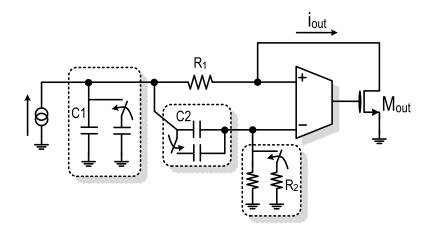

| 2.11 | RC filter inserted in the output current mirror of the V-I converter.                              | 39 |

| 2.12 | Effect of the RC filter on output current linearity                                                | 40 |

| 2.13 | Transmitter upconverter section: $N$ active mixers in parallel                                     | 41 |

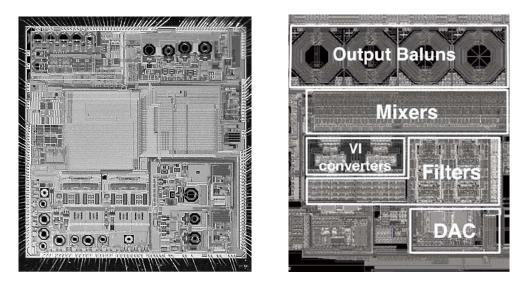

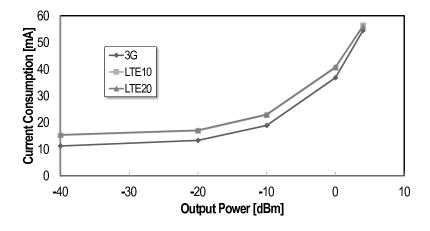

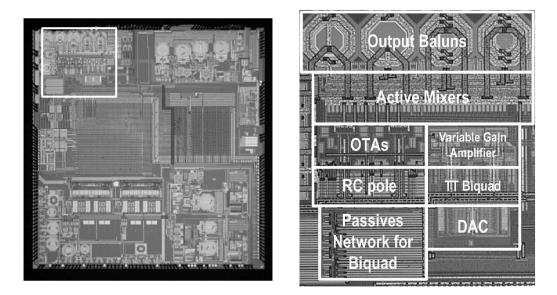

| 2.14 | Realized chip microphotograph (left) and detailed layout of the trans-<br>mitter (right)           | 42 |

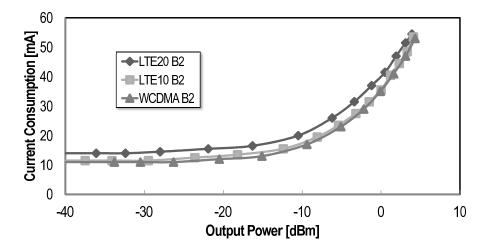

| 2.15 | Transmitter current consumption from $1.8V.\ldots\ldots\ldots\ldots$                               | 42 |

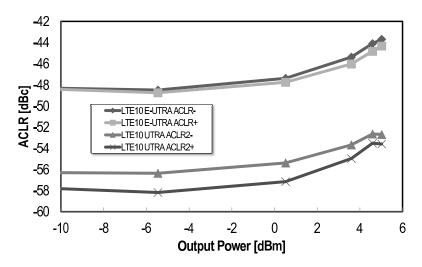

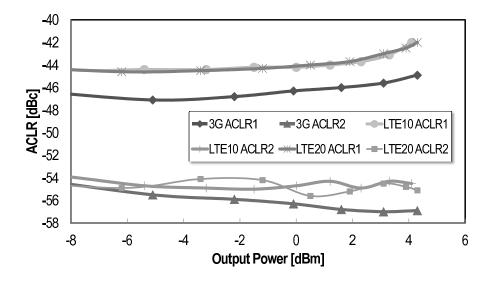

| 2.16 | Transmitter linearity parameters vs. output power transmitted                                      | 43 |

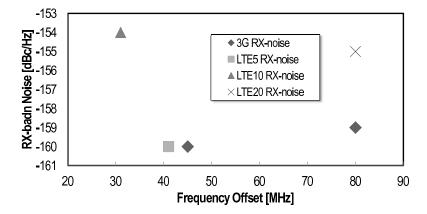

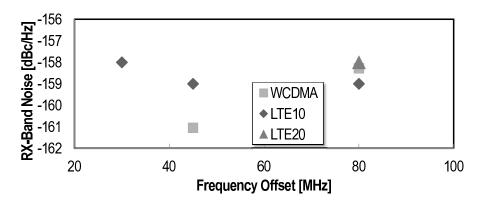

|      | Out-of-band noise performances vs. frequency offset from the RF carrier.                           | 44 |

|      |                                                                                                    |    |

| 3.1  | Moving the filtering block at the end of the baseband can improve                                  |    |

|      | noise and power consumption                                                                        | 48 |

| 3.2  | Block diagram of a full current-mode transmitter                                                   | 49 |

| 3.3  | Simplified schematic of a traditional mixed-mode transmitter baseband.                             | 50 |

| 3.4  | $Evolution from the mixed-mode to the current-mode transmitter. \ . \ .$                           | 51 |

| 3.5  | Simplified schematic of the implemented VGA                                                        | 52 |

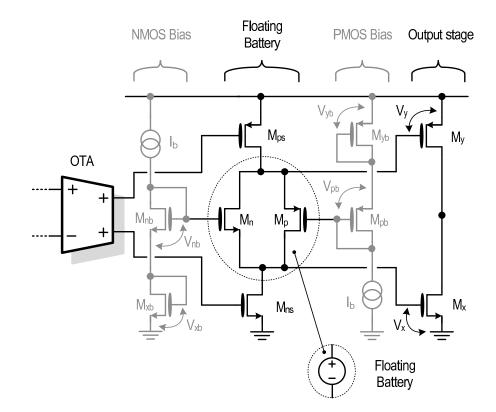

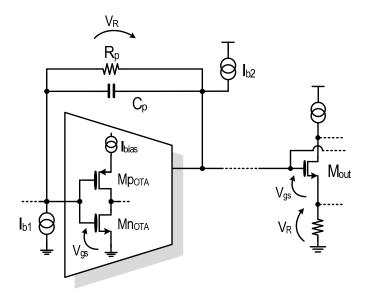

| 3.6  | Implementation of the floating battery in the OTA output stage                                     | 53 |

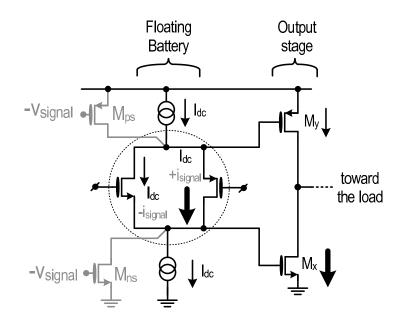

| 3.7  | Behaviour of the output stage with unbalanced signals                                              | 54 |

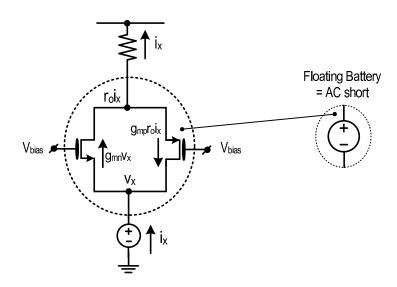

| 3.8  | Input impedance of the floating battery                                                            | 55 |

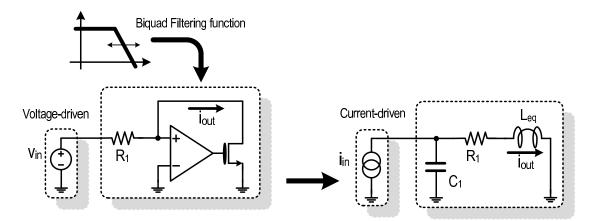

| 3.9  | Conceptual idea of transforming the V-I converter into a current-                                  |    |

|      | driven biquad filter                                                                               | 55 |

| 3.10 | Single-ended version of the current-driven biquad                                                  | 56 |

| 3.11 | $3^{rd}$ and $5^{th}$ order filtering configuration of the DAC+Additional Bi-<br>quad+VGA section. | 58 |

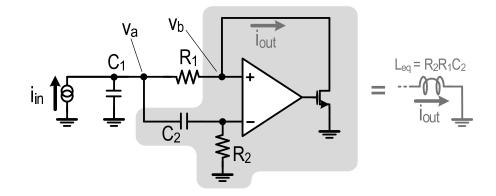

| 3.12 | Conceptual schematic of the DAC.                                                                   | 59 |

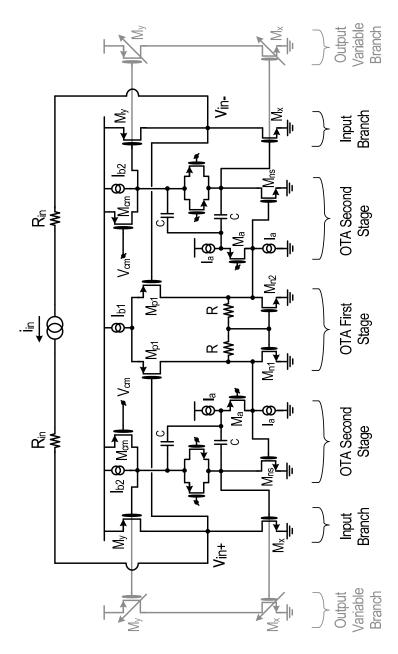

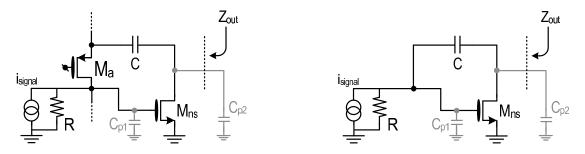

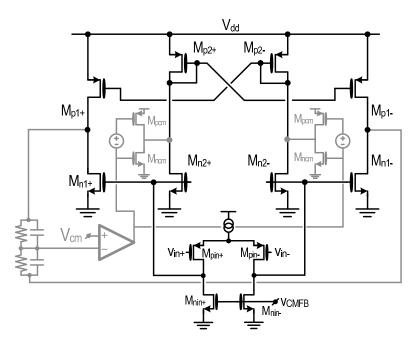

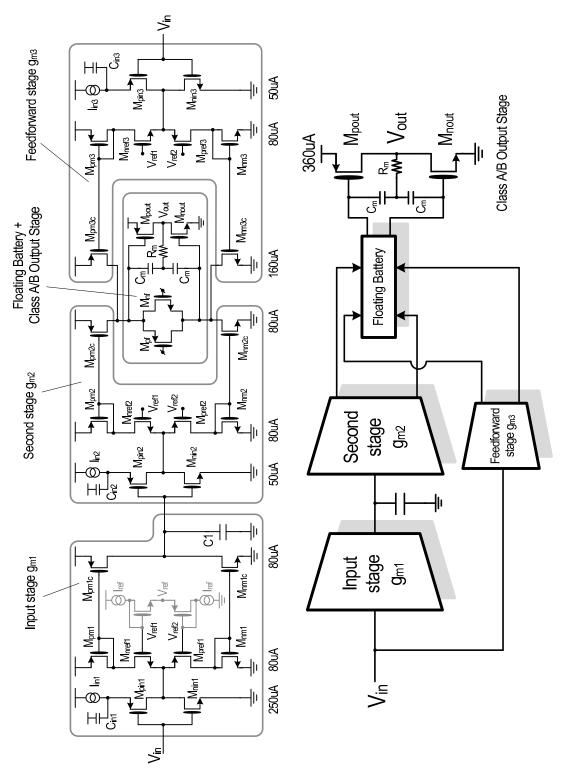

|      | Detailed implementation of the VGA OTA.                                                            | 61 |

|      | Comparison between Miller and Ahuja compensations.                                                 | 62 |

|      | Class $A/B$ working of the output stage                                                            | 62 |

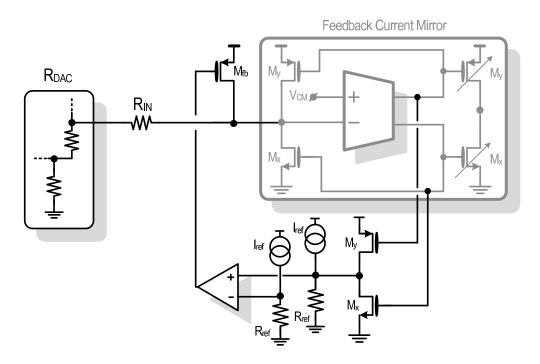

|      | Input feedback assuring the current for the DC voltage offset.                                     | 64 |

|      | DC biasing of the current-driven biquad.                                                           | 65 |

|      | Block diagram of the multipath OTA.                                                                | 67 |

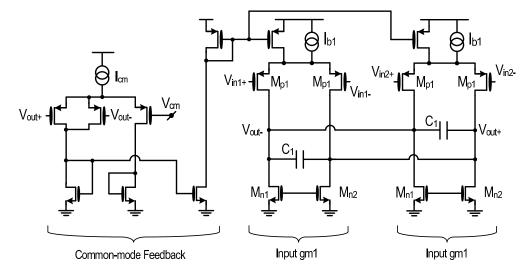

|      | Schematic of the input $gm_1$ of the OTA.                                                          | 67 |

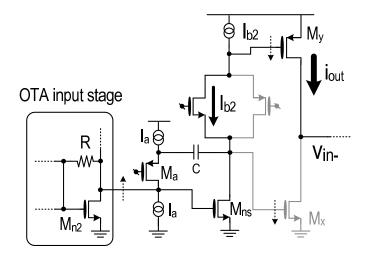

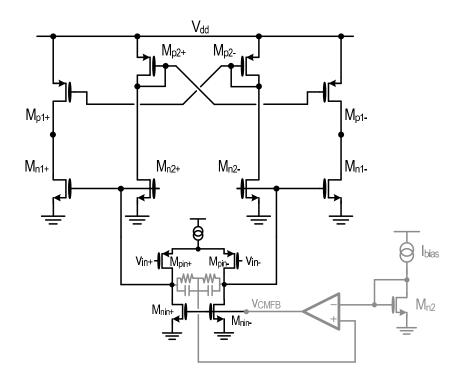

|      | Current common-mode feedback of the OTA output stage.                                              | 68 |

| 3.20 | Voltage common-mode feedback of the OTA output stage                                               | 68 |

|      | Passives reconfiguration of the current-driven biquad.                                             | 70 |

|      | Complete transceiver chip microphotograph (left) and transmitter                                   | 10 |

|      | details (right).                                                                                   | 71 |

| 3.24 |                                                                                                    |    |

|      | transmitted.                                                                                       | 72 |

| 3.25 | Transmitter linearity parameters vs. power transmitted                                             | 73 |

| 3.26 | Out-of-band noise performances vs. TX-RX frequency offset                                          | 73 |

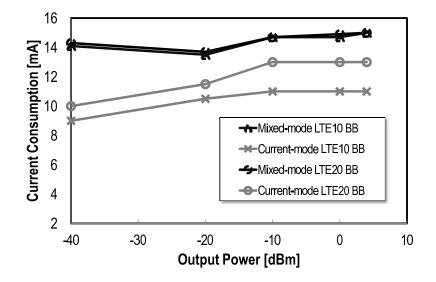

| 3.27 | Comparison of the baseband current consumptions.                                                   | 75 |

| 4.1  | Fundamental building blocks of a transmitter                                                       | 78 |

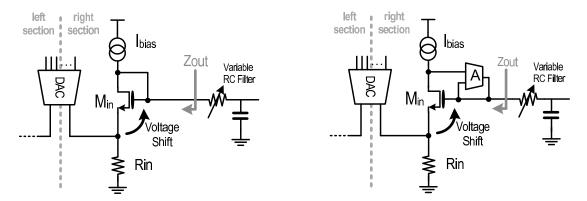

| 4.2  | Voltage shifter: without (left) and with (right) the OTA in feedback. | 80 |

|------|-----------------------------------------------------------------------|----|

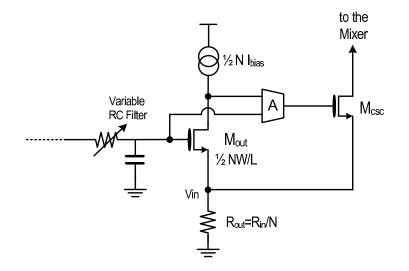

| 4.3  | Output stage driving the active mixer                                 | 81 |

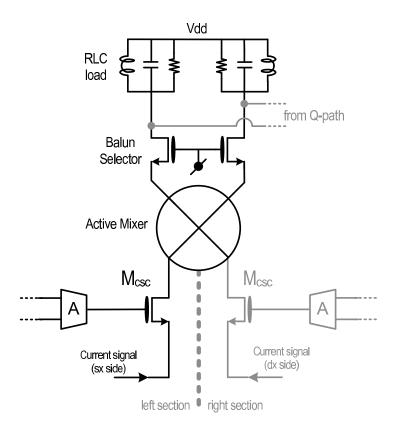

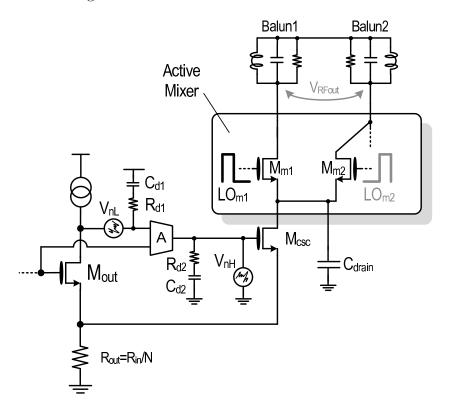

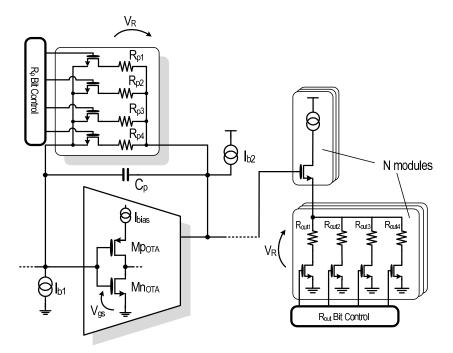

| 4.4  | RF section of the transmitter.                                        | 82 |

| 4.5  | Structure of the first OTA                                            | 83 |

| 4.6  | Block diagram of the output OTA                                       | 84 |

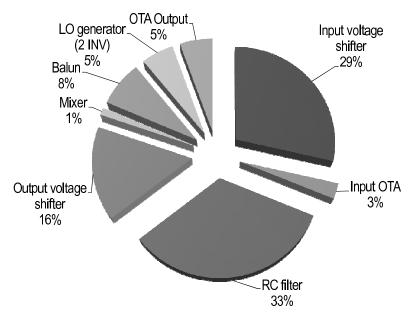

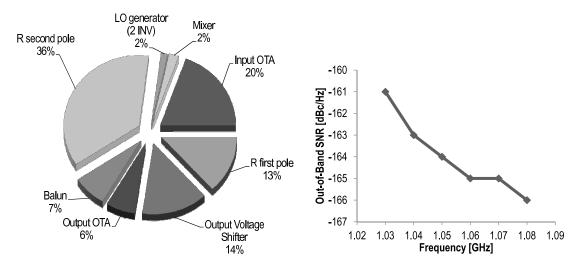

| 4.7  | Contributors percentage of the out-of-band noise                      | 86 |

| 4.8  | Transformation from a first to a second filtering order               | 88 |

| 4.9  | Matching of the output stage with the input stage of the OTA          | 89 |

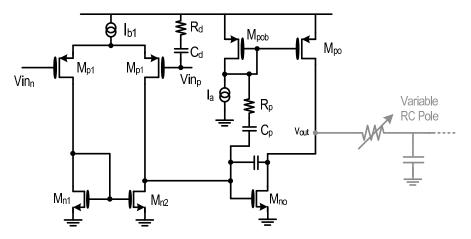

| 4.10 | Matching of the output stage with the input structure                 | 90 |

| 4.11 | Detailed schematic of the proposed input OTA                          | 91 |

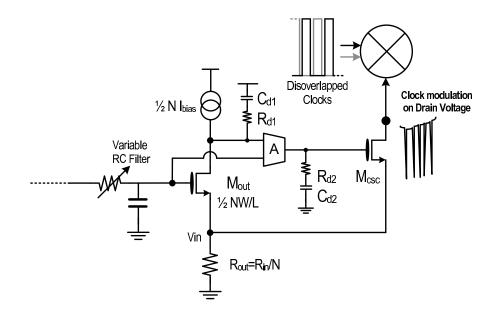

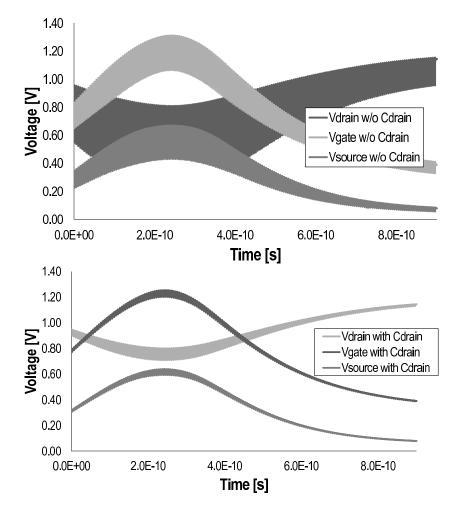

| 4.12 | Clock modulation of the output transistor drain.                      | 93 |

| 4.13 | Output noise from upconversion and from leakage                       | 94 |

| 4.14 | Filtering effect of the drain capacitor.                              | 95 |

| 4.15 | Resistor reconfigurability in the transmitter baseband                | 96 |

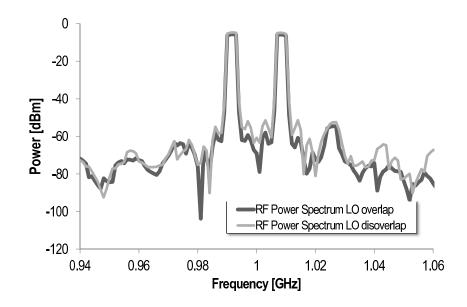

| 4.16 | RF power spectrum with and without LO disoverlap                      | 97 |

| 4.17 | RF out-of-band noise contributors and behaviour vs. frequency off-    |    |

|      | set from the carrier.                                                 | 97 |

|      |                                                                       |    |

## List of Tables

| 2.1 | Comparison with transmitter from ISSCC2012 [12]                                                                                    | 45 |

|-----|------------------------------------------------------------------------------------------------------------------------------------|----|

|     | Comparison with a voltage-mode transmitter from ISSCC2011 [9] .<br>Comparison with a current-mode transmitters from ISSCC2012 [12] | 74 |

| 0.2 | and Ch. 2                                                                                                                          | 75 |

|     | DC biasing of the transmitter                                                                                                      | 85 |

|     | band noise.                                                                                                                        | 87 |

### Chapter 1

# State-of-the-Art of Transmitters for Mobile Communications

The introduction of the new standard LTE for mobile communications, besides 2G and 3G, needs an improvement on many performances of modern transceivers. In this first Chapter, a basic description of the features of the 4Gstandard is given, together with the challenging aspects and the introduced issues. The characteristics of modern integrated transmitters for mobile applications and their design are then discussed, focusing in particular on the problem of out-of-band emission when removing the external SAW filter placed before the external Power Amplifier. An overview of the major contributors to outof-band emission is stated, along with the key figure of merit describing linearity, modulation accuracy and noise in transmitters. Finally, a summary of the State-of-the-Art of transmitters for mobile communications closes the Chapter.

### 1.1 An introduction to the Long-Term Evolution

The Long-Term Evolution, marked as 4G LTE, is the new standard for wireless communication of high-speed data for mobile phones and data terminals [1, 2]. Based on the GSM/EDGE and UMTS/HSPA network technologies, it increases the capacity and speed using a different radio interface together with enhancements in the core network. The standard has been developed by the 3GPP ( $3^{rd}$  Generation Partnership Project) like the previous standards and it is fully specified in his Release 8 documents.

LTE Release 8 was frozen in December 2008 and it has been the basis for the first wave of LTE equipment. The specifications are very stable and the motivations for the introduction of the new standard have been several:

- the need to ensure the continuity of competitiveness of the 3G system for the future;

- higher data rates and quality of service needed by the user;

- optimization of the Packet Switch system;

- cost reduction of the devices and services;

- the need for low complexity.

#### 1.1.1 LTE Overview

The access part of LTE (or the E-UTRAN, Evolved Universal Terrestrial Access Network) is called the Evolved Packet System (EPS). High spectral efficiency, high peak data rates, short round trip time and frequency flexibility are the new and main requirements for the EPS.

During the '90s, GSM was studied to carry real time services, with data services only possible over a circuit switched modem connection, with very low data rates. The first step towards an IP based packet switched solution was made with the evolution from GSM to GPRS, using the same air interface and access method, TDMA (Time Division Multiple Access). Finally, the Universal Mobile Telecommunications System (UMTS) was developed with a new access network, based on CDMA (Code Division Multiple Access), to reach higher data rates and data volume. The circuit switched connection and a packet switched connection for datacom services are emulated in the access network in UMTS for real time services. Moreover, the IP address is allocated when a datacom service is established and released when the service is released. However, incoming datacom services are still relying upon the circuit switched core for paging.

The core network is also prepared to be compatible with other access technologies not introduced by 3GPP, like WiMAX and WiFi. Non-3GPP developed access solutions are separeted in trusted and non-trusted: this division is not based merely on the technical solution, but only on the business relation/agreement between the operators.

The new Evolved Packet System is purely IP based: real time services and datacom services are carried by the IP protocol. The IP address is allocated when the mobile is switched on and released when switched off. LTE is able to reach even higher data rates and data volumes compared to the previous standards. High order modulation (up to 64QAM), large bandwidth (up to 20MHz, starting from 1.4MHz) and Multiple Input Multiple Output (MIMO) transmission in the downlink is also a part of the solution. The highest theoretical data rate is 170Mbps in uplink and, with MIMO approach, the rate can reach 300Mbps in the downlink.

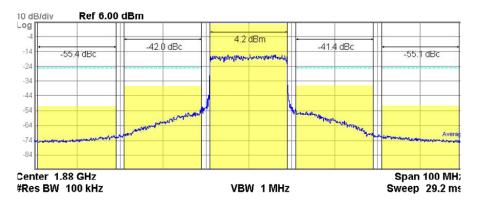

The 3GPP chose a multicarrier approach for multiple access to achieve very high spectral efficiency. Orthogonal Frequency Division Multiple Access (OFDMA) was selected for the downlink. OFDM, a multicarrier technology that subdivides the available signal bandwidth into many mutual orthogonal narrowband subcarriers, also shares these subcarriers with multiple users. With this solution, it is possible to exploit variations in both frequency and time domains, achieving very high spectral efficiency, but requiring fast processors. Furthermore, OFDMA solution leads to high Peak-to-Average Power Ratio (PAR), up to 9dB, requiring expensive and demanding power amplifiers with severe requirements on linearity, increasing the battery consumption. This would lead to very expensive handsets. To compensate for these problems, the uplink of LTE uses OFDMA and the Single-Carrier Frequency-Division Multiple Access (SC-FDMA), a precoded version of OFDM, also known as Discrete Fourier Transform (DFT) spread OFDMA, depending on the channel. To allow possible deployment around the globe and to support as many regulatory requirements as possible, LTE is developed for many frequency bands, ranging from 800MHz up to 3.5GHz and numbered from Band1 to Band44. The available bandwidths are also very flexible, starting with 1.4MHz up to 20MHz. As an example, in Fig. 1.1 is reported an RF LTE20 spectrum, taken from a spectrum analyzer. As we can see, the bandwidth is very well defined (20MHz) and the signal power is flat inside the band.

LTE supports both Frequency-division duplex (FDD) and Time-division duplex (TDD) modes: FDD uses paired spectra for uplink and downlink transmission separated by a duplex frequency gap and TDD separates one frequency carrier into alternating time periods for transmission from the base stations to the terminals and viceversa. The two modes have their own frame structure and these are aligned with each other, i.e. similar hardware can be used in the base stations and terminals to allow the scaling-down approach. These days, a single chipset can support both TDD-LTE and FDD-LTE operating modes.

FIGURE 1.1: LTE20 signal spectrum, taken from a Spectrum Analyzer.

In the time domain, the LTE transmission is structured in radio frames. Each of these radio frames is 10ms long and consists of 10 subframes of 1ms each. In the frequency domain, the OFDM subcarrier spacing is 15kHz. Twelve of these subcarriers together are called a Resource Block (RB): e.g., LTE10 full spectrum consists of 50 RB while LTE20 of 100 RB. However, in the downlink or uplink channel a minimum of 1 Resource Block during 1 subframe can be allocated.

Given that LTE provides high spectral efficiency with high data rates and a flexible access architecture, it will become a success among operators as well as customers.

### 1.2 Out-of-Band emission and modern transmitter parameters

#### **1.2.1** General considerations

Integrated terminals for the new standard 4G are very demanding, since they also have to be compatible with all the pre-existing communication standards and, moreover, with many other wireless standards (WiMAX, WLAN, GPS etc...): nowadays, this is the trend in smartphone design. The most critical situation of coexistance is always the one of a receiver and a transmitter that are working in a FDD operation on the same mobile device. In fact, if we look to a typical mask of interferers for mobile communications FDD standards when designing a front-end, we can see that one of the most critical interferer is given from the transmitter itself.

3G and 4G standards, that require receiver (RX) and transmitter (TX) working at the same time on different bands, suffer from this issue. A partial isolation between the two paths is given by the duplexer: the two inputs have different passband transfer functions toward the ouput, so the RX and the TX can work at the same time, while the path between them is isolated. This property protect the most sensitive part of a transceiver, i.e. the analog front-end, from the emission in the RX signal band coming from the transmitter. Anyway, the isolation is not infinite, and leakage from the transmitter propagates in the RX-path.

There are two type of problem arising from this leakage and, with the use of large signal bandwidths as the ones of the 4G, these problems become even more critical:

- linearity: the wanted small received signal has to cohabitate with many interferers and the biggest one is coming from the transmitter itself, even if attenuated: the analog processing of the RX-path can create non-linearities and intermodulations that can fall in the received bandwidth, corrupting the wanted signal or saturating the receiver. Dealing with these interferences issues is, however, the duty of the receiver;

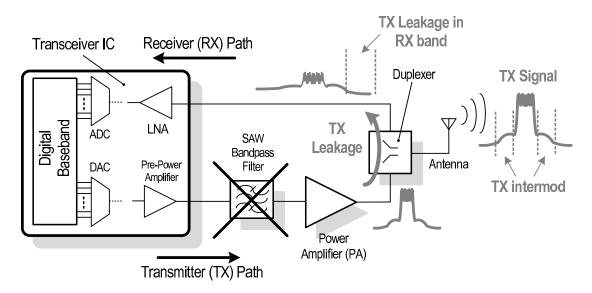

- out-of-band emission (see Fig. 1.2) : the transmitted signal and his leakage will be attenuated by the duplexer, but the leakage residuals that lie in the RX-band directly impact the performances of the receiver, since it is added

to the noise floor given from the the antenna and the noise figure. Moreover, out-of-band noise is also an important concern for coexistence of cellular transmitters with standards like GPS, WLAN and/or WiMAX on the same smartphone, a very common scenario nowadays. Finally, attention must be paid also to linearity issues (i.e. out-of-band intermodulations) that can impact other radio systems around the device.

This last problem is traditionally resolved using a SAW filter at the ouput of the integrated transmitter and before the Power Amplifier (PA) as shown in Fig. 1.2. The drawback is that the SAW filter is a bulky, external and expensive element on the cellular phone board. Furthermore, among the 44 working Bands mentioned before, each SAW filter can handle only some of them since they are manufactured to be effective only for narrowbands: hence, many of them, centered at different frequencies, are placed on the board.

FIGURE 1.2: A typical block diagram of a transceiver.

Nowadays, since the mobile hand-set must move toward an entire reconfigurable and integrated radio transceiver, the trend is to eliminate this blocks, not reconfigurable and not integrable: with this goal, the transmitter must provide a very low out-of-band emission. In fact, with the 3G, it was possible to eliminate the SAW filters. However, the introduction of LTE forced the designers to re-introduce the SAW filter for some critical working bands, where the signal bandwidth is large and hence the frequency distance between the RX-band and the TX-band is very small. Beside the issues with the receiver, the low emissions are also necessary because the transmitted signal must cohabitate with other standards that exist at other frequencies without interfere with them.

Three elements coming from the baseband of a transmitter are the principal contributors to the out-of-band emission: the DAC replicas, out-of-band noise and non-linearity. In the following sections, we're gonna discuss these elements and, in general, the main parameters of a transmitter for mobile communications.

#### **1.2.2 DAC Replicas**

The analog section of a transceiver is the part that interface the signal with the world. The baseband processing of the signal is, instead, entirely digital. Hence, an Analog to Digital Converter (ADC) is necessary in the receiver chain while a Digital to Analog Converter (DAC) is the interface of the transmitter chain (see Fig. 1.2).

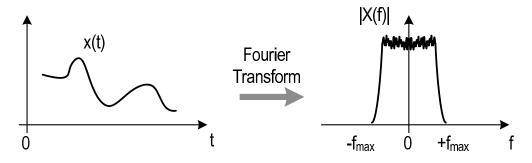

In the transmitter, the band-limited signal x(t) with spectral components beyond a frequency  $f_{max}$  equal to zero (like the one in Fig. 1.3) can be completely reconstructed from a set of uniformely spaced discrete-time samples, given from the digital baseband to the DAC, if the samples are taken with a sampling rate  $f_s$ ,

$$f_s \ge 2f_{max}.\tag{1.1}$$

This is known as the uniform sampling theorem and the sampling rate  $f_s = 2f_{max}$  is called the Nyquist rate [4].

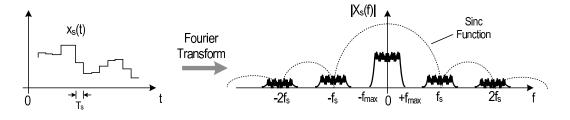

Suppose an analog waveform x(t) with a Fourier Transform X(f) equal to zero for  $|f| > f_{max}$  (Fig. 1.3) and sampled in the time domain. Ideally, sampling x(t)

FIGURE 1.3: A time-domain signal x(t) and his Fourier Transform X(f) in the frequency domain.

means taking the product of x(t) with a periodic train of impulse functions  $x_{\delta}(t)$ , defined as

$$x_{\delta}(t) = \sum_{n=-\infty}^{+\infty} \delta(t - nT_s), \qquad (1.2)$$

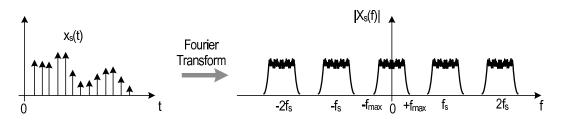

where  $T_s = 1/f_s$  is the sampling period and  $\delta(t)$  is the Dirac delta function [3]. In Fig. 1.4 is reported the sampled version of x(t), denoted as  $x_s(t)$ . It can be expressed as

$$x_{s}(t) = x(t)x_{\delta}(t) = \sum_{n=-\infty}^{+\infty} x(t)\delta(t - nT_{s}) = \sum_{n=-\infty}^{+\infty} x(nT_{s})\delta(t - nT_{s}).$$

(1.3)

The signal spectrum of  $x_s(t)$  can be obtained from Eq. 1.3. In fact, using convolution [3], the Fourier transform of the sampled signal  $X_s(f)$  can be rewritten as the convolution of  $X_f$  and the Fourier transform of  $x_{\delta}(t)$   $(X_{\delta}(f))$ :

$$X_{s}(f) = X(f) * X_{\delta}(f) = X(f) * \left[\frac{1}{T} \sum_{n = -\infty}^{+\infty} \delta(f - nf_{s})\right] = \frac{1}{T} \sum_{n = -\infty}^{+\infty} X(f - nf_{s}),$$

(1.4)

using the frequency domain form of the impulse train:

$$X_{\delta}(f) = \frac{1}{T_s} \sum_{n=-\infty}^{+\infty} \delta(f - nf_s).$$

(1.5)

The spectrum  $X_s(f)$  of  $x_s(t)$  is exactly the same as  $X_f$  of the original signal x(t), to within a constant factor  $(1/T_s)$ . Moreover, the spectrum repeats itself in frequency every  $f_s$ , as depicted in Fig. 1.4.

FIGURE 1.4: Signal x(t) sampled in the time-domain and his spectrum.

A real DAC is not able to provide ideal impulses at his output. In fact, his output can be seen as an impulse followed by a sample and hold that keeps the value of the impulse for a period of  $T_s$ . The mathematical representation is the convolution of the sampled impulse train  $x(t)x_{\delta}(t)$  with a unity amplitude rectangular pulse p(t) of width  $T_s$ :

$$x_{s}(t) = p(t) * [x(t)x_{\delta}(t)] = p(t) * \left[x(t)\sum_{n=-\infty}^{+\infty} \delta(t-nT_{s})\right].$$

(1.6)

This results in the function represented in Fig. 1.5. His Fourier transform is the product of the Fourier transform P(f) of the rectangular pulse and the spectrum of the impulse sampled sequence:

$$X_{s}(f) = P(f) \frac{1}{T_{s}} \sum_{n=-\infty}^{+\infty} X(f - nf_{s}), \qquad (1.7)$$

where P(f) is the cardinal sinus  $P(f) = T_s sinc(fT_s)$ . As we can see in Fig. 1.5, the signal replicas at multiples of the sampling frequencies are now filtered through a sinc function.

FIGURE 1.5: Output signal of a real DAC and his spectrum

However, this filtering is usually not sufficient, since the replicas could fall, when transmitted, in other bandwidth where other standards are or where the receiver (integrated on the same chip) is working. Of course, increasing the DAC sampling rate  $f_s$  would push the replicas at higher frequency, but at power consumption costs.

Hence, the usual strategy in transmitter chains is to insert a filtering block (usually with high-order) that eliminate the DAC replicas and it is traditionally place right after the converter.

#### 1.2.3 Out-of-band noise

While in receivers the in-band noise is an issue, in transmitters is the noise out-ofband. We already mentioned that the high-frequency noise leakage of the transmitter passes through the duplexer into the RX-band and can degrade the performances of the receiver. Of course, since there are many operating bands with different TX-RX frequency offsets, the worse situations will be where the offset is small and when the bandwidth of the signal is large (the bandwidth of the noise will be large too, since it depends on the signal processed).

The traditional strategy was to put a SAW filter before the Power Amplifier (PA) to eliminate this leakage, but nowadays the trend is to eliminate these SAW blocks to save costs. Hence, the transmitter must be very low-noise and this could be achieved by changing the structure and optimizing the filtering in the TX chain. For example, a filter is already implemented to attenuate the DAC replicas, but it eliminates also the out-of-band-noise coming from the DAC, since it contributes with thermal noise and with quantization noise. The filter could be useful also to eliminate the high-frequency noise coming not only from the DAC but also from the entire baseband chain. Typically, beside the filtering block already introduced for the DAC replicas and noise, another filtering block is added expecially for out-of-band noise of the other blocks.

FIGURE 1.6: Numerical example of out-of-band noise requirement calculations for a transmitter.

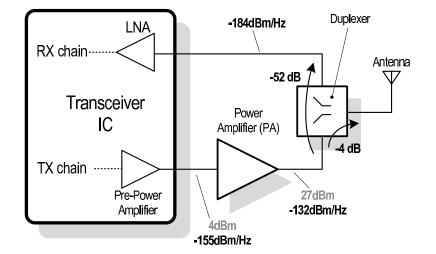

An example of the calculation of the requirement for the out-of band noise is given in Fig. 1.6. The noise floor of a receiver, supposing matched input impedance, is given by

$$10Log\left(\frac{kTR_a}{50\Omega \cdot 1mW}\right) = -174dBm/Hz,\tag{1.8}$$

where k is the Boltzmann constant, T the room temperature in Kelvin and  $R_a$ the antenna resistance (= 50 $\Omega$ ). Supposing that the transmitter leakage must not contribute too much to this noise, his level will be 10dB lower, i.e. -184dBm/Hz. Supposing, moreover, that the duplexer has an attenuation from TX to RX of -52dB and that the Power Amplifier gain is +23dB, we get that the required outof-band noise for the transmitter is -155dBm/Hz when the pre-power amplifier in the IC is emitting 4dBm. The measurement of this parameter is made with respect to the carrier of the transmitted signal, hence as a signal-to-noise ratio (SNR): the requirement for the transmitter is a SNR of -159dBc/Hz.

FIGURE 1.7: Out-of-band noise meaurements testbench.

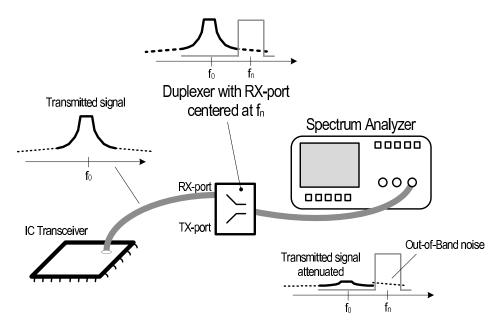

When measuring the noise performances of an integrated transmitter, the usual procedure is the following: the RF output is connected to a spectrum analyzer through the duplexer RX-port accorded to the signal carrier. Hence, the stop-band of the duplexer attenuates the transmitted signal, while the noise in the RX-band will pass unchanged (except for the insertion loss) and it can be measured without saturating the spectrum analyzer with the huge transmitted signal.

The procedure is described in Fig. 1.7. The noise is calculated as an integral in the RX-bandwidth and an equivalent noise density is extracted (in dBm/Hz).

Then, moving the IC output probe in the TX-port of the duplexer, it is possible to measure the transmitted power and hence the Signal-to-Noise Ratio (in dBc/Hz).

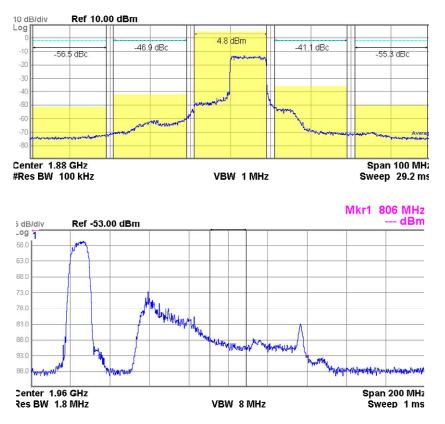

The 3GPP usually provides specific situations for the noise measurements. For what concerns 3G, the measure is done using the usual signal, occupying a 3.84MHz RF bandwidth. For the 4G, where the signals have a bandwidth more large, the signal used for the test is made of partial Resource Blocks (RBs) instead of the full signal: the number of the used RBs depends on the TX-RX offset. The RBs are positioned on the side of the measured noise. An example of partial signal is reported in the spectrum analyzer screenshots of Fig. 1.8, on top: specifically, it's the signal used for noise measurements for LTE20 in Band2 (centered at 1.88GHz). As we can see, the signal is made of 50 RBs placed on the right side of the carrier

FIGURE 1.8: LTE20 signal spectrum (from a spectrum analyzer) used for outof-band noise measurements and, below, transmitted signal spectrum through the RX-port of a duplexer.

and the noise will be measured at +80MHz offset, i.e. at 1.96GHz, near the RBs. In the second screenshot of Fig. 1.8, instead, the measured noise on the spectrum analyzer screen is reported: the high power burst, centered at 1.88GHz, is the transmitted signal attenuated by the duplexer. A bandwidth of 18MHz around 1.96GHz is taken and an equivalent noise density extracted. Once the power transmitted is known, it is possible to calculate the SNR in dBc/Hz. Notice the shape of the noise: it is following a first-order filtering roll-off, since the noise in that transmitter was filtered in the baseband with and RC filter. Moreover, it should be noticed that, in this kind of measurements, it is usually very difficult to dicriminate between noise and non-linearities: in fact, when large signals are transmitted, also non-linearities (i.e. ACLR, see the following section) contribute to noise. In Fig. 1.8 also some digital spurious tones are also evident, but this is an issue related to the digital baseband and signal routing.

Finally, the major contributors to the out-of-band noise are divided into baseband contributors and pre-power amplifier contributors. Since, as we'll see, the last stage of the on-chip transmitter is a programmable stage to control and increase the output power, when the transmitted power is toward the maximum possible value, the major contribution is coming from the programmable stage driver, since his output signal and noise are amplified. On the contrary, when the output power is scaled down, also the pre-power amplifier is scaled down and his noise contribution starts to be significant and, at very low power, it dominates the total SNR.

#### **1.2.4** Non-linearities considerations: ACLR

The Adjacent Channel Leakage Ratio (ACLR or ACPR, Adjacent Channel Power Ratio) is basically the measure of the linearity of the transmitter [4, 5]. Unwanted emissions from mobile transmitters are usually tightly restricted so as not to interfere with other radio systems. Among emission specifications, the most important ones are the emission levels in the adjacent and the alternate channels and thery are strictly controlled in wireless mobile systems. The adjacent/alternate channel emission power specification is generally defined as the ratio of the power integrated over an assigned bandwidth in the adjacent/alternate channel to the total desired transmission power. The expression is

$$ACLR = \frac{\int_{f_0 - \Delta BW/2}^{f_0 + \Delta BW/2} PSD(f)df}{\int_{f_0 - \Delta BW/2}^{f_0 - \Delta BW/2} PSD(f)df},$$

(1.9)

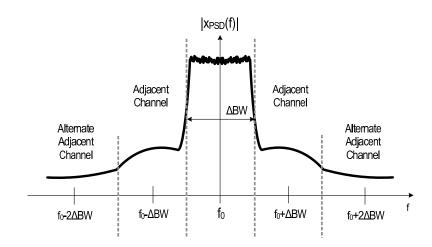

where PSD(f) is the Power Spectrum Density of the transmitted signal, while the other variables are reported in Fig. 1.9. A similar expression is given for the alternate ACLR.

FIGURE 1.9: Definitions of adjacent and alternate adjacent channels in a transmitted signal spectrum.

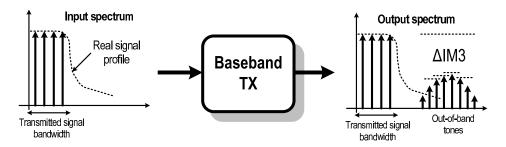

The adjacent/alternate channel powers mainly result from spectral regrowth and non-linearity coming from the Pre-Power Amplifier in the IC transmitter and the Power Amplifier itself. In Cadence simulations, it is usually complicated to simulate a real modulated signal, hence a multitone signal is used. It is possible to emulate both the PAR and also the RMS of the real modulated signal with a multitone test and then evaluate the IIP3 of the circuit. The behaviour with the real modulated signal can be extracted with an expression that connects the IIP3 to the ACLR [6]. A simplified ACLR can be simulated with this multitone test, calculating the ratio between the signal tones and his out-of-band intermodulations (a kind of  $\Delta IM3$  simulation, as seen in Fig. 1.10 for a baseband signal).

FIGURE 1.10: Qualitative linearity definition through a 4-tones simulation.

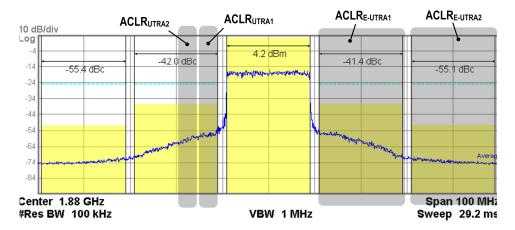

For what concerns LTE, there are some distinctions in the ACLR parameters: since the standard has to cohabitate with himself, but also with 3G, 2G and other standards like GPS etc..., distinctions between  $ACLR_{E-UTRA}$  and  $ACLR_{UTRA}$  are made. Without going too much in details, the definitions are reported in Fig. 1.11 for an LTE20 signal with 100 RBs. As we can see, the UTRA ACLR are more related to the cohexistance of LTE with narrow bandwidths, like the 3G, while the E-UTRA is for larger bandwidths.

FIGURE 1.11: ACLR<sub>UTRA</sub> and ACLR<sub>E-UTRA</sub> definitions on the transmitted signal spectrum.

#### 1.2.5 Error Vector Magnitude

Another parameter of transmitted signals is the modulation accuracy, that will ensure an optimum conversion when the signal will be received. The modulation accuracy is represented by the Error Vector Magnitude (EVM) [4], that is the difference between the actual symbol location and the theoretical symbol location on the modulation vector constellation diagram. As an example, in the CDMA downlink, offset QPSK (OQPSK) modulation [5, 4, 7] is used for the PN spreading code because of power and spectrum efficiency consideration. The bandpass signal with OQPSK modulation can be expressed with an in-phase and a quadrature signal as:

$$s(t) = a_I(t)cos(\omega_c t) - a_Q(t)sin(\omega_c t)$$

(1.10)

where  $a_Q(t)$  and  $a_I(t)$  are the amplitudes of the in-phase and the quadrature signals, respectively,

$$a_I(t) = \sqrt{2}A \sum_{k=-\infty}^{+\infty} I_k g(t-kT_c), \qquad a_Q(t) = \sqrt{2}A \sum_{k=-\infty}^{+\infty} Q_k g(t-kT_c-T_c/2).$$

(1.11)

In these equations, A is the modulation signal amplitude,  $I_k$  and  $Q_k$  are the I and Q PN sequences with value 1 or -1 that are mapped from the I and Q spread data PN sequences 0 and 1, respectively.  $T_c$  is the PN chips duration and g(t) is the

time domain response of the pulse shaping filter [4], that is a rectangular pulse before the pulse shaping,  $g(t) = g_r(t)$  written as

$$g_r(t) = \begin{cases} 1 & 0 \le t < T_c \\ 0 & \text{elsewhere} \end{cases}$$

(1.12)

Introducing a discrete time variable with a time step  $T_c/2$  (half chip duration) instead of the continuous time variable and using Eq. 1.10, the baseband modulation I/Q signal calculated at  $t = k_1 T_c/2$  from Eq. 1.11 and Eq. 1.12 we obtain the following:

$$a_I(k_1) = A\cos[\phi(k_1)], \qquad a_Q(k_1) = A\sin[\phi(k_1)], \qquad (1.13)$$

where  $k_1$  denotes the time instant  $k_1T_c/2$  and the modulation angle  $\phi(k_1)$  is determined the the PN mapping [4]. The modulation can also be expressed in a vector form:

$$\overline{a}(k_1) = \overline{a_I}(k_1) - j\overline{a_Q}(k_1) = Aexp^{\phi(k_1)}$$

(1.14)

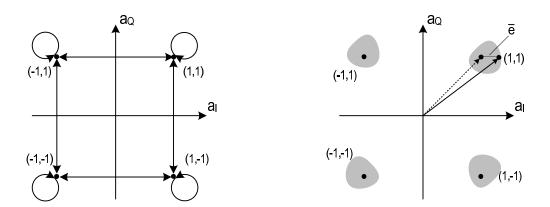

and this permits to have an intuitive geometrical interpretation with the signal constellation [7], depicted Fig. 1.12.

The modulation is generally distorted by phase noise of the Local Oscillator (LO) when it upconverts the RF carrier. Furthermore, it will be degraded when the signal passes through a narrow-bandwidth filter due to the magnitude ripple and the group delay of the filter. Thus, the distorted modulation  $\overline{a'}(k_1)$  can be expressed as

$$\overline{a'}(k_1) = \overline{a}(k_1) + \overline{e}(k_1), \qquad (1.15)$$

where  $\overline{e}(k)$  represents the residual error vector. The constellation diagram of the distorted modulation vector is depicted in Fig. 1.12.

The modulation accuracy is represented by the Error Vector Magnitude (EVM) and it is defined as the mean square error between the samples of the actual and the ideal signals, normalized by the average power of the ideal signal. The EVM can be represented as

$$EVM = \left[\frac{E\{|\overline{a}'(k_1) - \overline{a}(k_1)|^2\}}{E\{|\overline{a}(k_1)|^2\}}\right]^{1/2} = \left[\frac{E\{|\overline{e}(k_1)|^2\}}{E\{|\overline{a}(k_1)|^2\}}\right]^{1/2},$$

(1.16)

FIGURE 1.12: Signal constellation of a QPSK modulation: ideal (left) and distorted with EVM (right)

where  $E\{\cdot\}$  represents the expectation of ensemble averages and the values are usually expressed in %. The maximum tolerable EVM is usually around 10% at the antenna, after the external Power Amplifier.

### **1.3** State-of-the-Art Transmitters

Now that we have discussed about the major problems and parameters of a transmitter, we can deduct the three "natural" elements that are necessary in an analog baseband chain. First, the DAC: the interface with the digital baseband is fundamental. Second, a filtering block: this one will eliminate the out-of-band noise and the DAC replicas. His position must be right before the upconversion to eliminate the most of the out-of-band emission before going to RF. Third, a Variable Gain Amplifier (VGA): actually, this last block is not a mandatory block, but it is necessary from an engineering standpoint. It will be necessary to reconfigure the output power of the transmitter to meet the various requirements. His function can be reparted in many other blocks: usually, there can be some programmability in the digital baseband, in the DAC itself, in the RF section with the pre-power amplifier but also another explicit block in the baseband.

In the next sections we will see how these functions are implemented in some example of transmitters coming from the state-of-the-art.

#### 1.3.1 Cassia [8]

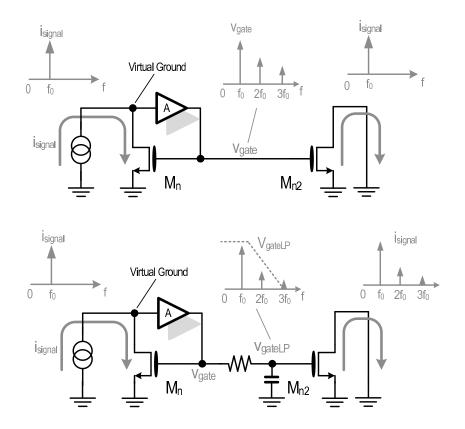

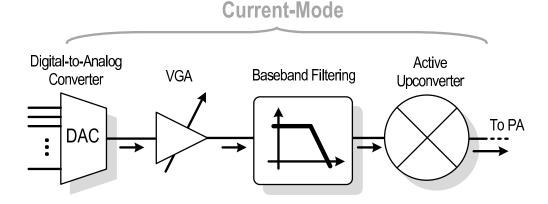

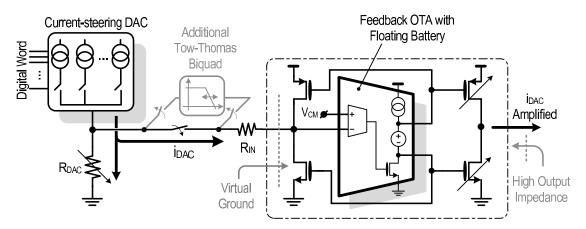

In this work from ESSCIRC 2008, a multi-band CMOS transmitter for cellular applications (in particular, 2G and 3G) is presented. The transmitter covers a wide range of frequency bands and it is designed to minimize power consumption in order to increase hand-set talk time. The external baseband I/Q differential current signals are injected into the baseband filter. Common mode input voltage and input impedance are set by an input buffer: it is crucial to keep a low commonmode voltage as well as low impedance to allow low voltage operations. After the filter, the signal is mirrored to the up-converters with a variable mirror factor  $G_{bbvga}$ , filtered, passed through a RF amplifier and transferred to a driver amplifier with a balun.

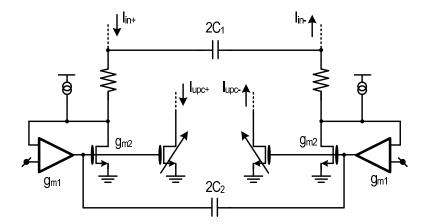

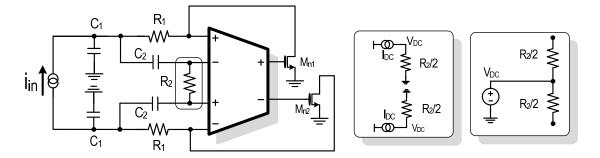

The purpose of the baseband filtering is to eliminate the DAC replicas and his sampling noise and attenuate out-of-band noise in the receiver bandwidth. The filter bandwidth is reprogrammable from 1MHz to 5.6MHz and a simplified schematic is shown in Fig. 1.13. The transconductors  $g_{m1}$ ,  $g_{m2}$  and the capacitor  $C_2$  form an

FIGURE 1.13: Baseband filtering in current-mode proposed by [8].

active inductor providing an overall second order low-pass transfer function:

$$I_{upc}(s) = I_{in}G_{bbvga} \frac{1}{(\frac{s}{\omega_0})^2 + (\frac{s}{\omega_0 Q}) + 1},$$

(1.17)

where  $I_{in}$  is the input current and  $G_{bbvga}$  is the current mirror factor. The resonant frequency  $\omega_0$  and the Q factor can be expressed as:

$$\omega_0 = \sqrt{\frac{g_{m1}g_{m2}}{C_1 C_2}}, \qquad \qquad Q = \frac{1}{R} \sqrt{\frac{C_2}{C_1 g_{m1} g_{m2}}}.$$

(1.18)

With this filter, the transmitter meets the requirements for the elimination of the external SAW filter.

The upconverter is made of a traditional active Gilbert cell. The in-phase baseband signal is upconverted with the in-phase LO signal and the quadrature baseband signal is upconverted with the quadrature RF LO signal. The mixer outputs are summed and the resulting differential signal is passed through a variable attenuator at RF.

The transmitter (excluding the frequency synthesizer) operates from a 2.1V supply and the total TX power consumption (including the synthesizer) is around 120mWfor an ouput power of 5dBm and 90mW for -8dBm. Besides low WCDMA power consumption, output noise performance allows SAW-filter removal across several frequency bands. The measured sensitivity in SAW-less mode is still below -110dBm.

The transmitter from [8] shows a complete current-mode approach in the baseband: the input signal is a current and the analog processing (filtering, upconversion and amplification) is operated in the current domain. The filter parameters, anyway, are related to MOS transconductance  $(g_m)$  values. Since, to improve the signal-tonoise ratio (SNR), the signal swing is usually maximized (as we'll discuss later), the  $g_m$  varies substantially with the signal level. Time-variance of  $g_m$  makes the filter signal-dependent causing distortion and degrading the EVM. In fact, the EVM performances for 3G are around 5%. The instantaneous  $g_m$  variance can be substantially higher in the 4G standard, where the Peak-to-Average Ratio (PAR) is 3dB higher than the 3G.

#### 1.3.2 Giannini [9, 10]

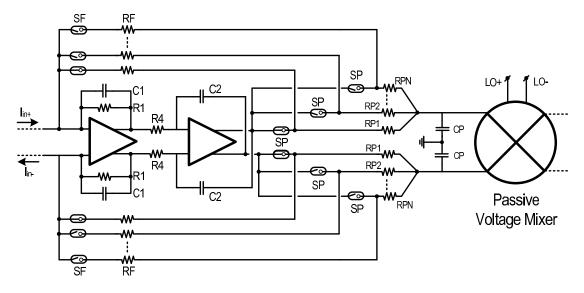

This work from ISSCC 2011 is a multi-standard transmitter LTE-oriented. His approach is the dual of the previous one, since in this one a voltage-mode approach is used: instead of an active Gilbert mixer, where the current signal is switched, a voltage passive-mixer is introduced (as proposed originally from [11]), and instead of a baseband filter that provides a filtered current, a more traditional Tow-Thomas biquad (see Ch. 2) with a voltage output is employed.

Fig. 1.14 shows the block diagram of the presented transmitter: a  $3^{rd}$ -order transimpedance low-pass filter (TILPF) (made up of a biquad plus a RC pole) removes the DAC replicas and out-of-band noise. The TILPF is followed by a passive mixer which upconverts the baseband voltage on the pre-power-amplifier's (PPA) input capacitor.

FIGURE 1.14: Baseband filtering in voltage-mode with a passive voltage mixer, proposed by [9].

The TILPF design is based on a flexible Tow-Thomas topology that offers independent programming of transimpedance gain, bandwidth and Q factor, whereas a quadrature voltage sampling mixer performs the upconversion using a low-noise 25%-duty-cycle LO driver. Filtering and mixing stages are designed to limit the impact on the transmitter Carrier-to-Noise Ratio (CNR) while keeping the power consumption minimal over the required RF range. At baseband, to achieve out-ofband noise lower than -180dBm/Hz with limited power consumption, a passive LPF is added after the TILPF. From a system perspective, good CNR and high output power over different bands can be achieved with a tuneable passive pole.

To avoid linearity degradation, the switches of the RP array are closed inside a multi-feedback loop generated from the previous filtering stage, as shown in Fig. 1.14. When an SP switch is ON to activate a certain resistor RPx, a corresponding feedback loop is selected through the switch SF and feedback resistor RF. The nonlinear resistance of the active SP switch is thus divided by the open loop gain of the TILPF making his contribution to the distortion negligible. Overall the passive pole bandwidth can be moved from 7MHz up to 50MHz. In order to efficiently drive RP values as low as  $40\Omega$ , a Class-AB op-amp topology is implemented that can trade power consumption for linearity. The transmitter consumes 13 to 44mA from the 1.1V supply (TILPF + LO generation) depending on the selected bandwidth and LO frequency, whereas the PPA consumes less than 43mA from the 2.5V (PPA), proportionally to the required output power and linearity.

Notice that the PPA's input capacitor can be a serious issue due to the switched capacitor effect that force the capacitor of the passive filter RC to be very large. This means a large area occupied and a high power consumption, since this capacitor has to be driven in order to prevent slew-rate. Moreover, the fact that I and Q are summed on a voltage node lead to crosstalking of the two paths if the LO are not perfectly disoverlapped. In fact, the effect of this is the presence of a "bending" in the spectrum of the transmitted signal, as it can be seen in the snapshots in the original paper [9].

Finally, the proposed measurements of out-of-band are taken as Carrier-to-Noise Ratio, i.e. the SNR when the TX is transmitting an in-band single tone. With this method, the effect of non-linearities and the noise bandwidth spreading is not actuated, hence the numbers can be very low, since they are related only to the noise floor of the transmitter.

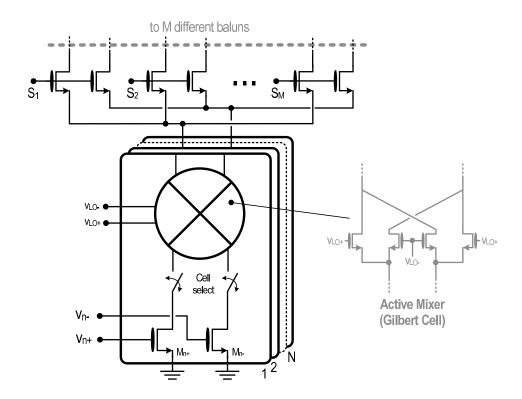

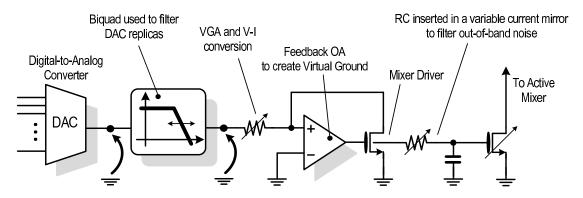

#### 1.3.3 Oliaei [12]

The previous discussed work on LTE has mainly focused on the stringent RX-band noise and ACLR requirements for SAW-less transmitter design without discussing the Counter-InterModulation (CIM) performances. OFDM modulation in LTE20 creates up to 100 Resource Blocks (RB) (as discussed in the introduction) each containing 12 subcarriers with 15kHz spacing, spread over the channel bandwidth. For an RB with frequency offset  $f_s$  from the LO, transmitter non-linearity causes CIM products at  $-3f_s$ ,  $+5f_s$ ,  $-7f_s$ , ... from the LO. These spurious signals directly, or through remixing due to PA non-linearity, may fall on other bands. The worst case is when one or just a few RBs are transmitted at the edge of the channel. CIM terms are first generated by mixers. A pre-power amplifier (PPA) placed after the mixers will cause these terms to be regenerated due to high-level harmonic sidebands.

This example from ISSCC 2012 is a multimode multiband PPA-less transmitter which meets the counter-intermodulation and RX-band noise requirements for

SAW-less operation for 2G, 3G and 4G. The transmitter analog section is repre-

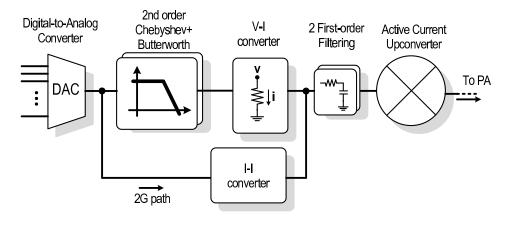

FIGURE 1.15: Analog transmitter section diagram block proposed by [12]

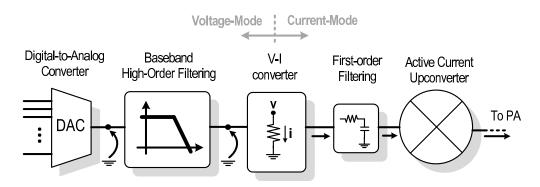

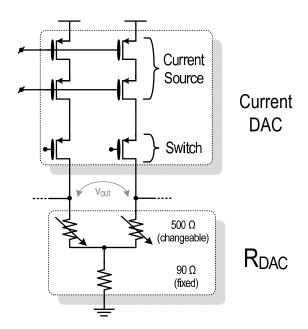

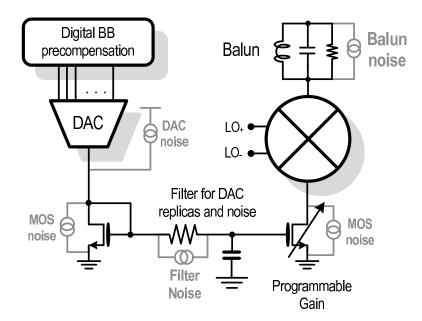

sented in Fig. 1.15. The digitally modulated TX signal is converted into analog using a 12-bit current-mode DAC and subsequently transformed into voltage by the baseband filter (BBF) for 3G and 4G signals. The DAC rate is selectable between 62.4MHz and 249.6MHz. The BBF is a cascade of two  $2^{nd}$ -order Butterworth and Chebychev filters to achieve enough quantization noise attenuation and DAC image rejection while maintaining a small group-delay variation and magnitude flatness over the signal bandwidth. The BBF output is converted into current using a voltage-to-current converter (V-I) which also incorporates two cascaded passive RC filters to reject the noise generated by the BBF. The DAC output is directed to a current-to-current converter (I-I) for 2G signals. The V-I (3G/4G) path is designed for high linearity while the I-I (2G) path is optimized for noise performance.

The RF section of the transmitter consists of four separate paths corresponding to four band groups. Only one RF path is activated at any time. The V-I and I-I outputs are routed to current-mode IQ mixers for frequency upconversion. Current-mode mixing has been selected mainly to reduce the CIM effect and avoid the need for digital pre-distortion. The upconverted signal is attenuated using a passive Variable Gain Amplifier (VGA) and eventually delivered to a tuned balun to drive the external PA.

The transmitter draws a maximum current of 52mA and 32.8mA from, respectively, 2.7V (upconverter) and 1.55V (baseband) supplies to generate 4dBm linear output power in LTE20. Notice that a 2.7V has been chosen to achieve a large output swing since the entire output section is working in Class A. The transmitter shows a total power consumption of 186mW and 199mW when emitting 4dBm in LTE10 and LTE20, respectively, dominated by the RF section. The out-of-band noise is instead -155dBc/Hz at 30MHz offset for LTE10 and -157dBc/Hz at 120MHz offset for LTE20.

This transmitter is an example of a mixed-mode working. The previous works were entirely voltage-mode or current-mode: this one instead keeps the voltagemode in the baseband and a current-mode for the upconversion, needing hence a V-I converter.

### 1.4 Conclusions

In the first part of this Chapter an introductory description of the new standard LTE has been given, together with the new problems that arise with it. In particular, the challenges are related to the transmitter's analog section of the integrated transceiver, that must interface the signal from the digital baseband with the antenna. These challenges gathers the issue of out-of-band emission, constituted of DAC replicas, noise and non-linearity, but also issues for the in-band signal, defined by the EVM. Finally, a survey on the State-of-the-Art for transmitters is given in the last part of the Chapter, taken from recent conferences and journals.

## Chapter 2

# An LTE Transmitter using a Class A/B Power Mixer

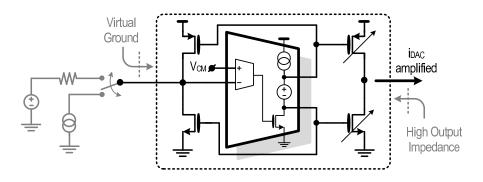

Moving toward the antenna side of the transmitter, the power consumption becomes more and more higher and it is critical to improve the efficiency of the last stages, without compromising the noise performances. In this Chapter, a fully reconfigurable multi-standard transmitter is presented that introduces a high-efficiency active mixer. The transmitter is operated in voltage-mode for the baseband (DAC plus two Biquad cells), while a power mixer is adopted for the upconversion. The two domain are interfaced with a V-I converter that implements also a variable gain. Moreover, the V-I converter drives the mixer in Class A/B through a particular architecture of the output stage. The realized chip and the measurements will be presented in the last part of the Chapter.

## 2.1 Voltage-mode Baseband

#### 2.1.1 General Block Diagram

As seen in the examples from the State-of-the-Art presented in Ch. 1, there can be two approach in the design of a transmitter (but, of course, also in electronics in general), each one with pros and cons: a voltage-mode and a current-mode.

In the transmitter here presented [17], a voltage-mode has been adopted for the baseband, while a power mixer (and so a current-mode approach) is used for the upconversion of the baseband signal to RF. The block diagram of the entire analog baseband chain is shown in Fig. 2.1 and it is quite similar to the one presented in Fig. 1.15 from [12]. The stage that connects the two modes of operation is a V-I converter and it also acts as an active mixer driver, since the converted current will be mirrored into the switching pair (as described further). Notice that a filter (a real pole) is placed between these two blocks to eliminate out-of-band noise coming from the V-I converter and the high-order filtering block.

Moving upstream, the voltage-mode section is made of a 10-bit current-steering segmented DAC that steers the current signal on a resistor and his voltage drop is fed at the input of a high-order filter. Observe that in Figure 2.1 a very general block diagram is reported: indeed, although the described DAC is intrinsically a current DAC, the fact that the signal is transformed immediately into a voltage to fed the following filter makes it actually a voltage DAC, and so it is represented in the block diagram.

FIGURE 2.1: Block schematic of the Multistandard Transmitter

One of the major problem in transmitters for mobile communications, as already pointed out in Ch. 1, is the out-of-band emission: this is constituted by DAC replicas, noise and non-linearities. In the next sections we'll see how this transmitter deals with all these issues.

## 2.1.2 High-Order Filtering Block: the Tow-Thomas Biquad

Only in the LTE case, we have seen that there are many possible signal bandwidths (from 1.4MHz to 20MHz) and the other previous standards have bandwidths still different. It is not possible to have on the same chip a transmitter chain for each one: the area cost will explode, considering the fact that besides mobile communication standards other communication standards must be implemented in the same transceiver (WLAN, Bluetooth, GPS etc...). Hence, a multi-standard transmitter must be reconfigurable and adaptive to optimize his performances for each standard. Having the aforementioned different signal bandwidths, the filtering function (performed by the filter block before the V-I converter, but also by the real pole before the mixer in Fig. 2.1) must change his cut-off frequency to adapt to the processed bandwidth.

As already pointed out, the main role of the high-order filter is to eliminate the DAC replicas and noise, meanwhile the passive filter is necessary to eliminate the out-of-band noise of the remaining blocks before the upconversion. Two general observations can be made. First, the more sharper the filtering is, the more effective his function is, but the filter order is in trade-off with power consumption and area. Second, we'd like to put the cut-off frequency the closest possible to the signal bandwidth or even inside this bandwidth to increase his filtering effect on the out-of-band side. In this case two problem arises:

- the in-band spectrum of the signal is filtered and it should be pre-compensated in the digital baseband, before driving the DAC;

- the same goes for the phase of the signal: if the cut-off frequency is close to the edge of the bandwidth, the phase delay of the spectrum near the filter cut-off will be different from the spectrum in the low frequency and this could lead to EVM problems.

Of course, if it is possible to pre-process the signal (amplitude and phase) in the digital baseband, there wouldn't be any problem. Otherwise, the filter cut-off frequency must be larger than the signal bandwidth.

The minimum filtering order in this transmitter is decided to be a Butterworth  $3^{rd}$  order and so the high-order filter must be a biquadratic cell, while the single real pole is already placed before the mixer. Among the voltage biquads architectures, the Tow-Thomas biquad is, from an engineering standpoint, one of the best solutions since it permits to configure gain, Q and  $\omega_0$  orthogonally. His topology is reported in Fig. 2.2.

FIGURE 2.2: Tow-Thomas Biquad schematic.

The input voltage  $v_{DAC}$  is transformed into a current through  $R_1$  thanks to the virtual ground created by the global feedback at the negative terminal of the first Op-Amp. It is then processed with the second integrator and the resistor  $R_3$ . The last sign inversion can be easily implemented in a fully differential configuration by crossing the differential output nets.

The transfer function from  $v_{DAC}$  to  $v_{out}$  is

$$\frac{v_{out}}{v_{DAC}} = \frac{G\omega_0^2}{s^2 + s\omega_0/Q + \omega_0^2}$$

(2.1)

where

$$\omega_0 = \frac{1}{\sqrt{R_3 R_4 C_1 C_2}}, \quad Q = \frac{R_2 \sqrt{C_1}}{\sqrt{R_4 R_3 C_2}}, \quad G = \frac{R_3}{R_1}.$$

(2.2)

A typical strategy is to put  $R_4 = R_3 = R$  and  $C_1 = C_2 = C$ , after which Eq.s 2.2 simplifies to

$$\omega_0 = \frac{1}{RC}, \quad Q = \frac{R_2}{R}, \quad G = \frac{R}{R_1}.$$

(2.3)

As seen from Eq. 2.3, the three variables can be modified by changing just one element:  $\omega_0$  with C, Q with  $R_2$  and G with  $R_1$ . In the proposed solution, the capacitors are fixed and the resistor values are changed to adapt the cut-off frequency to the 2G, 3G and 4G. The Q of the biquad is changeable with  $R_2$ , making easily possible to change also the type of the low-pass filter (Butterworth, Chebyshev...).

## 2.1.3 Operational Amplifier (OA) vs. Operational Transconductance Amplifier (OTA)

Besides DAC replicas, another contributor to out-of-band injection is given by noise. The biquad itself, described before, will filter the DAC replicas and DAC noise, whereas his own noise and the one coming from the following V-I converter will be filtered by the real pole inserted downstream. To ensure that a firstorder will be sufficient to eliminate the most part of the out-of-band noise, the noise sources must be minimized and the Signal-to-Noise Ratio (SNR) must be maximized. The first one is directly related to the area occupied and to the power consumption [13]. The second one is achieved by maximizing the signal swing inside the circuit. In fact, in general, noise coming from many blocks of a circuit is loosely independent from the amplitude level of the processed signal (unless non-linearities, high swings or saturations occurr): whereas the noise is almost constant, to improve the SNR the signal level must then be increased as much as possible toward the rail-to-rail, limited by the power supplies.

The output stage of a traditional Operational Amplifier (OA), like the ones used for the Tow-Thomas in Fig. 2.2, is usually a source-follower with a low output impedance and it is unable to maximize the output voltage swing. In fact, as shown in Fig. 2.3, when the output voltage has to go over  $V_g - V_{th}$  (where  $V_{th}$ is the threshold of the output MOS), the transistor starts to turn off, leading to distortion in the signal. The low boundary in instead given by the  $V_{ov}$  of the current souce. On the contrary, an Operational Tranconductance Amplifier (OTA) output stage (Fig. 2.3, on the right) is able to reach almost a rail-to-rail swing (limited by the overdrive of the PMOS and the NMOS).

On the other hand, there are some other issues. Since the ouput stage is now a gain stage and not a buffer stage, when impedances lower than the output stage

FIGURE 2.3: On the left, a source follower used as output stage of an OA; on the right, an inverter as output stage of an OTA.

impedance are used in the feedback network <sup>1</sup>, the potential gain of the entire OTA is wasted. If, instead, higher impedances are used, a dominant pole could arise in the output stage, leading to issues in stability. However, in general, the gain loss is not a problem compared to the output signal swing and hence the use of an OTA is preferred. Lastly, even if it could be unusual to think of stages with high output impedance used in voltage-mode applications, we have to remember that they will be used in feedback, taking advantage of the effect of lowering the output impedances, provided that the gain loop is sufficient.

The Op Amp blocks reported in Fig. 2.2 are then actually implemented with OTAs, with the purpose of maximize the signal swings to improve the SNR.

### 2.1.4 Multipath OTA architecture

Large signal swings obtained with rail-to-rail operation make linearity another issue: the virtual grounds of the filter must be very good and hence the gain loop of the structure must be very high in the bandwidth of interest.

A traditional approach for the OTA is a dominant pole solution. Since the in-band gain must be high, the gain-product bandwidth must be positioned much more beyond the signal bandwidth of interest, as shown in Fig. 2.4. The maximum bandwidth of the desired baseband signal is 10MHz (LTE20), so we have to get a gain-bandwidth product around 1GHz to get a minimum open-loop gain of 40dBat 10MHz. The requirement of 1GHz gain-bandwidth product is not easy to achieve, taking into account stability issues due to corners, parasitic poles etc...

$<sup>^1\</sup>mathrm{That}'\mathrm{s}$  why OTA are usually suggested for architecture with capacitors in the feedback network [14].

FIGURE 2.4: Open-loop transfer function of an OTA with dominant pole approach (left) and with double-slope approach (right).

A more practical solution is a multipath OTA. The structure is based on the sum of two different paths, a low frequency path and a high frequency path that acts when the low frequency path gain is lower than his gain. Fig. 2.4, on the right, shows the transfer function. Two low frequency poles allow an initial slope of -40dB/dec instead of the ordinary -20dB/dec, so the gain drops quickily after those two dominant poles. When the low frequency gain path is lower than the gain of the high frequency path, this path becomes dominant and the global transfer function shows a zero that increase the phase. The 0dB-cross is with -20dB/dec: for the Bode cryterion [15, 16], the system will be stable if the OTA is placed in a buffer configuration. Moreover, the gain-bandwidth product will be less than the one of a dominant pole topology, allowing more robustness against parasitic poles, temperatures and process corners.

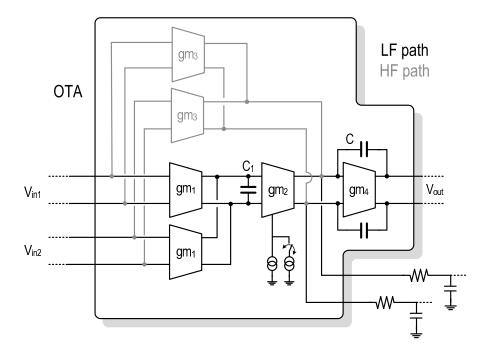

FIGURE 2.5: Block diagram of a multipath OTA.

Fig. 2.5 shows how to implement this transfer function. Two gm stages  $(gm_1 \text{ and } gm_2)$  constitute the low-frequency path while the single stage  $gm_3$  is the high-frequency path.  $gm_4$ , with the Miller capacitor C, is instead in common with the two paths. When the high-frequency path dominate the other, we can see that the first pole is "skipped". The low-frequency path  $H_{LF}(s)$  and the high-frequency

$H_{HF}(s)$  paths are defined as:

$$H_{LF}(s) = \left(\frac{gm_1R_1}{1+sC_1R_1}\right) \left(\frac{gm_2R}{1+sRC(1+gm_4R_4)}\right) (gm_4R_4), \qquad (2.4)$$

$$H_{HF}(s) = \left(\frac{gm_3R}{1 + sRC(1 + gm_4R_4)}\right)(gm_4R_4),$$

(2.5)