# University of Pavia

#### Ph.D. Thesis in Microelectronics

# Characterization and Modeling of Phase Change Memories

Author: Stefania Braga Advisors:

Prof. Guido Torelli

Ing. Alessandro Cabrini

Academic Year 2009/2010

To my family

# Contents

| In | trod                              | uction |                                             | 1  |  |  |

|----|-----------------------------------|--------|---------------------------------------------|----|--|--|

| 1  | Pha                               | se Ch  | ange Memories                               | 3  |  |  |

|    | 1.1                               |        | ing principle of the PCM cell               | 4  |  |  |

|    | 1.2                               |        | cell architectures                          |    |  |  |

|    | 1.3                               |        | change materials                            |    |  |  |

| 2  | Multilevel programming strategies |        |                                             |    |  |  |

|    | 2.1                               | Partia | al-RESET programming                        | 19 |  |  |

|    |                                   | 2.1.1  | Single-pulse partial-RESET programming      | 19 |  |  |

|    |                                   | 2.1.2  | Staircase-up partial-RESET programming      | 22 |  |  |

|    |                                   | 2.1.3  | Array analysis of SCU programming           | 26 |  |  |

|    | 2.2                               | Partia | al-SET programming                          | 36 |  |  |

|    |                                   | 2.2.1  | Single-pulse programming                    | 36 |  |  |

|    |                                   | 2.2.2  | Staircase-up voltage programming            | 41 |  |  |

|    |                                   | 2.2.3  | Staircase-up current programming            | 43 |  |  |

|    |                                   | 2.2.4  | Array analysis of partial-SET programming   | 48 |  |  |

| 3  | Cor                               | npact  | modeling of a PCM cell                      | 53 |  |  |

|    | 3.1                               | Analy  | tical model of the partial-RESET operation  | 54 |  |  |

|    |                                   | 3.1.1  | Experimental validation                     | 60 |  |  |

|    | 3.2                               | Dynai  | mic effects in partial-RESET programming    | 63 |  |  |

|    |                                   | 3.2.1  | Experimental validation                     | 71 |  |  |

| 4  | Pro                               | gramn  | ned resistance stability                    | 74 |  |  |

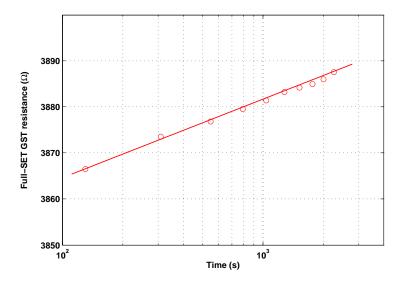

|    | 4.1                               | Low-f  | ield resistance drift                       | 75 |  |  |

|    |                                   | 4.1.1  | Partial-RESET states                        | 75 |  |  |

|    |                                   | 4.1.2  | Partial-SET states                          | 81 |  |  |

|    | 4.2                               | Cryst  | allization in partial-SET states            | 87 |  |  |

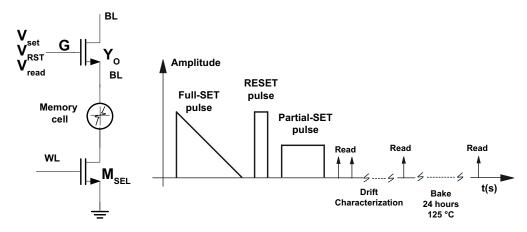

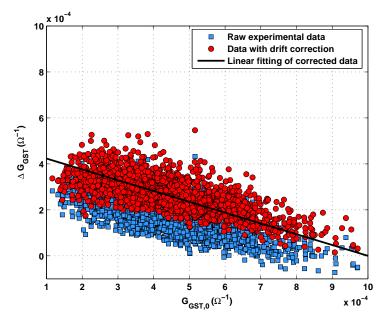

|    |                                   | 4.2.1  | Experimental procedure and drift correction | 88 |  |  |

|    |                                   | 4.2.2  | Stability of partial-SET states             | 92 |  |  |

| 5                    | Scaling of programming current and read window |                       |       |  |  |  |  |

|----------------------|------------------------------------------------|-----------------------|-------|--|--|--|--|

|                      | 5.1                                            | Programming operation | . 97  |  |  |  |  |

|                      | 5.2                                            | Read operation        | . 103 |  |  |  |  |

| Co                   | onclu                                          | asions                | 110   |  |  |  |  |

| General bibliography |                                                |                       |       |  |  |  |  |

# Introduction

Nowadays, non-volatile storage technologies play a fundamental role in the semiconductor memory market due to the widespread use of portable devices such as digital cameras, MP3 players, smartphones, and personal computers, which require ever increasing memory capacity to improve their performance. Although, at present, Flash memory is by far the dominant semiconductor non-volatile storage technology, the aggressive scaling aiming at reducing the cost per bit has recently brought the floating-gate storage concept to its technological limit. In fact, data retention and reliability of floating-gate based memories are related to the thickness of the gate oxide, which becomes thinner and thinner with increasing downscaling [1].

The above limit has pushed the semiconductor industry to invest on alternatives to Flash memory technology, such as magnetic memory (MRAM), ferroelectric memory (FeRAM), oxide memory (OxRAM) and phase change memory (PCM) [2, 3]. The last technology is one of the most interesting candidates due to high read/write speed, bit-level alterability, high data retention, high endurance, good compatibility with CMOS fabrication process, and potential of better scalability. However, it still requires strong efforts to be optimized in order to compete with Flash technology from the cost and the performance viewpoints.

In PCMs, information is stored by exploiting two different solid-state phases (namely, the amorphous and the crystalline phase) of a chalcogenide alloy, which have different electrical resistivity (more specifically, the resistivity is high for the amorphous phase and lower for the crystalline phase). Phase transition is a reversible phenomenon, which is achieved by stimulating the cell by means of adequate thermal pulses induced by applying electrical pulses. Reading the resistance of any programmed cell is achieved by sensing the current flowing through the chalcogenide alloy under predetermined bias voltage conditions. The read window, that is, the range from the minimum (amorphous state, RESET) and the maximum (crystalline state, SET) read current, is considerably wide, which allows safe storage of an information bit in the cell and also opens the way to the multi-level (ML) approach to achieve low-cost high-density storage. ML storage consists in programming the memory cell to one in a plurality of intermediate resistance (i.e., of read

current) levels inside the available window, which allows storing more than one bit per cell (the number of bits that can be stored in a single cell is  $n = log_2 m$ , where m is the number of programmable levels). The programming power and the read window depend on the electrical properties of the cell materials as well as on the architecture and the size of the memory cell. As the fabrication technology scales down the cell dimensions, new challenges arise to accurately program the cell to intermediate states and discriminate adjacent resistance levels.

In this framework, the aim of this Thesis is to investigate ML programming capabilities in PCM cells. Chapter 1 introduces the working principles and basic properties of PCM cells. In Chapter 2, experimental characterization is carried out to optimize the ML programming procedure, whereas an analytical model for partial-RESET programming with the capability of evaluating the effects of various parameters in this programming approach is developed in Chapter 3. The stability issues in intermediate states are studied in Chapter 4. In Chapter 5, the dependence of programming and read performances on the key geometrical parameters of the cell is addressed, in order to investigate the effects of technology scaling on the memory cell performance.

# Phase Change Memories

Besides Flash memory technology, which is based on the floating gate concept [4, 5], alternative non-volatile memory technologies based on innovative materials have been developed in last years. Among them, it is worth citing magnetic memory (MRAM), ferroelectric memory (FeRAM), and phase change memory (PCM) [2, 3].

The characteristics of such new memory technologies are compared to the features of Flash memories in Table 1.1 [2].

From this Table, PCM technology turns out to be one of the most interesting candidates among innovative memory technologies. In fact, PCMs present very small cell size with respect to MRAMs and FeRAMs, and much better scalability. The endurance, although lower than in the cases of FeRAM and MRAM, is still high if compared to Flash memories. In addition, it is

Table 1.1: Non-volatile memories characteristics

|                           | Flash     | Flash    | FeRAM     | MRAM      | PCM       |

|---------------------------|-----------|----------|-----------|-----------|-----------|

|                           | NOR       | NAND     |           |           |           |

| Cell feature size $(F^2)$ | 10-12     | 4-5      | 18        | 10-20     | 5-8       |

| Endurance (cycles)        | $10^{5}$  | $10^{5}$ | $10^{16}$ | $10^{14}$ | $10^{12}$ |

| Additional mask step      | 6-8       | 6–8      | 2         | 4         | 3–4       |

| Read speed                | 10 ns     | 50 ns    | 40 ns     | 50 ns     | 50 ns     |

| Write speed               | $2 \mu s$ | 500 ns   | 40 ns     | 50 ns     | 50 ns     |

| Read voltage              | 2 V       | 5 V      | 1.5 V     | 3.3 V     | 0.4 V     |

| Write voltage             | 12 V      | 18 V     | 1.5 V     | 3.3 V     | 1 V       |

| Direct overwriting        | No        | No       | Yes       | Yes       | Yes       |

| Programming energy        | High      | Medium-  | Low       | Medium    | Medium    |

|                           |           | High     |           |           |           |

worth remembering that PCM technology has a good compatibility with CMOS fabrication process, unlike FeRAM and MRAM technologies, which require the integration of ferroelectric and magnetic materials within the CMOS process. Few mask steps are required for PCM technology. Regarding the programming performances, PCM increases the write speed by at least one order of magnitude with respect to Flash memories, and is suitable for very low-voltage technologies.

The above described properties of PCM technology promise a wide range of potential applications. For instance, PCM may well address the NOR Flash market. In fact, PCM has about half the cell size, much faster programming, read time on the same order of magnitude and better endurance than NOR Flash. Concerning NAND Flash applications, such as solid-states drives, more efforts are needed to reduce the cell size and improve the multilevel capabilities of PCM, in order to reduce the cost per bit. However, PCM may also be used in DRAM applications, since non-volatility helps to reduce power consumption. The choice of a suitable memory architecture has been demonstrated to mitigate the main drawbacks of PCM technology as a DRAM alternative, such as high latency, high energy required for writing, and limited endurance [6].

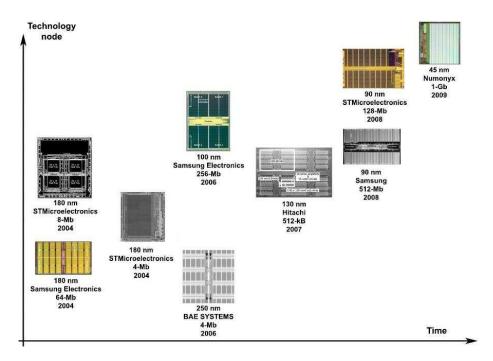

Among the companies that have invested in PCM technology it is worth mentioning Micron (formerly Numonyx, STMicroelectronics), Samsung Electronics, IBM, NXP, BAE Systems, and Hitachi. The developed PCM chips are shown in Fig. 1.1 [7, 8, 9, 10, 11, 12, 13, 14, 15].

### 1.1 Working principle of the PCM cell

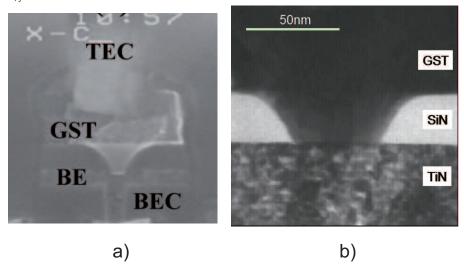

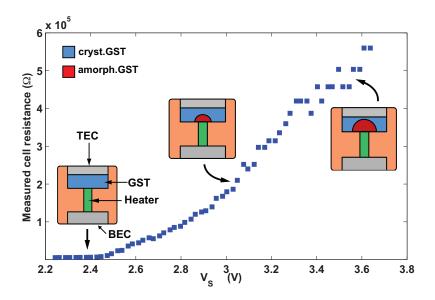

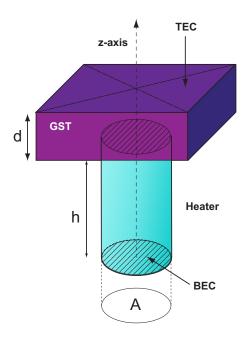

The working principle of a PCM cell relies on the physical properties of chalcogenide materials, that can switch from the amorphous to the crystalline phase and vice versa when stimulated by suitable electrical pulses. Basically, a PCM cell is composed of a thin chalcogenide film (usually  $Ge_2Te_2Sb_5$ , or GST), a resistive element named heater (typically made of TiN), and two metal electrodes, i.e., the top electrode contact (TEC) and the bottom electrode contact (BEC). Since phase transitions are thermally assisted, in PCM devices Joule heating is exploited to raise the temperature inside the chalco-

Figure 1.1: Technology roadmap for PCM development.

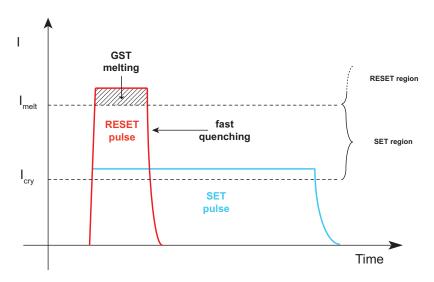

Figure 1.2: Standard pulses for bi-level PCM programming.

genide material to the required value. The crystalline-to-amorphous phase

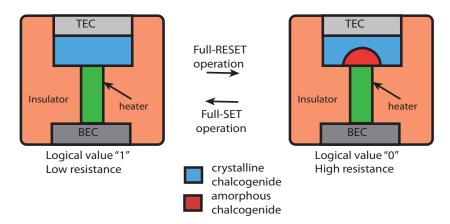

Figure 1.3: Conceptual scheme of a PCM cell in the full-SET and full-RESET states.

transition is obtained by applying a high-amplitude electrical pulse to the cell so as to bring the temperature of the active phase-change material above the melting point  $T_{melt}$  (about 600 °C for the GST alloy) [16], and then quickly cooling the memory cell, in order to freeze the chalcogenide material into a disordered (i.e., amorphous) structure. A pulse duration on the order of few tenth of ns is typically sufficient to crystallize the chalcogenide [17]. The amorphous-to-crystalline phase transition is obtained by applying an electrical pulse with a lower amplitude and a longer time duration than in the previous case. Then, the amorphous chalcogenide is heated to a temperature below the melting point but above the crystallization temperature, that is the temperature required to activate the crystallization process within the required time scale (typically on the order of 100 ns). This way, the thermal energy enables to restore the crystalline lattice, which is a minimum-energy structural configuration. Typical electrical pulses for SET and RESET operations are shown in Fig. 1.2. The obtained phase configuration is schematically depicted in Fig. 1.3.

Only a portion of the phase-change layer, which is located close to the GST-heater interface and is referred to as active chalcogenide, undergoes phase transition when the PCM cell is thermally stimulated. The phase state of the active chalcogenide determines the value of the memory cell resistance: the crystalline state corresponds to the minimum resistance (full-SET, logic

value 1), whereas the amorphous state corresponds to the maximum resistance (full-RESET, logic value 0) of the memory cell.

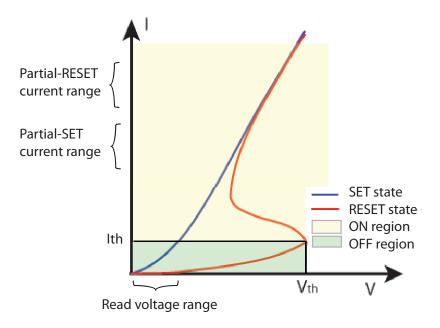

The typical V-I characteristics of the PCM cell in the SET and RESET states are shown in Fig. 1.4. Consider the case of a cell in its full-SET state: the differential resistance of the cell decreases as the applied voltage increases. This effect is due to the contribution of the crystalline chalcogenide to the cell resistance. In fact, typically the crystalline chalcogenide resistivity decreases with increasing electrical field inside the material.

The V-I curve of the cell in its RESET state shows an S-shaped behavior. This effect is due to the threshold switching phenomenon [18, 19, 20, 21], which consists in a sudden drop of the amorphous chalcogenide resistivity as the voltage across the PCM cell exceeds a critical value, typically referred to as threshold voltage,  $V_{th}$  (or, equivalently, when the current flowing though the cell exceeds the threshold value,  $I_{th}$ ). Thus, when low-amplitude voltage pulses are applied to the cell, a low current flows through the device, which is in its high-resistance state (OFF region in Fig. 1.4). On the other hand, when a high-amplitude voltage pulse is applied to the cell, threshold switching takes place and the device shows a much lower resistance (ON region in Fig. 1.4). Threshold switching in chalcogenide alloys is crucial for the feasibility of PCM technology. In fact, without threshold switching very high voltage pulses would be necessary to deliver enough power to the device to activate phase transition. Thanks to threshold switching, only few volts are required for programming despite the very high resistance of the cell in the OFF region. It is worth noticing that the V-I curves of the cell in the two states (SET and RESET) are essentially superimposed in the ON region, whereas they show substantial difference in the OFF region. Writing is carried out by operating the cell in the ON region, in order to provide the device with enough energy to induce phase change. On the other hand, readout must be carried out by operating the cell in the OFF region. Typically, a predetermined read voltage is applied to the cell and the current flowing through the device, referred to as read current, is sensed (current sensing approach). The read voltage must be low enough to avoid unintentional modification of the cell contents due to unintended heating during readout.

The read window, that is, the range from the minimum (RESET) and the

Figure 1.4: V-I curve of a PCM device in the SET and the RESET state.

maximum (SET) read current, is considerably wide, which allows safe storage of an information bit in the cell and also opens the way to the multilevel (ML) approach to achieve low-cost high-density storage. However, critical issues must be addressed when implementing ML programming. Among them, it is worth mentioning the capability to program and read the memory cells with sufficiently high accuracy, the reproducibility of the programming operation, and the stability of programmed levels. Furthermore, an effective ML programming algorithm must be robust with respect to variations of parameters of the memory cell and the surrounding circuitry.

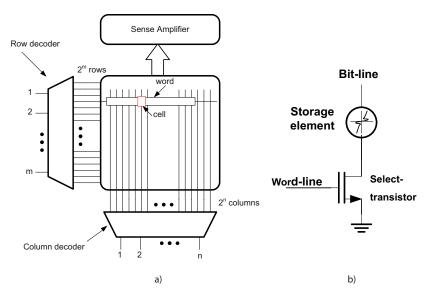

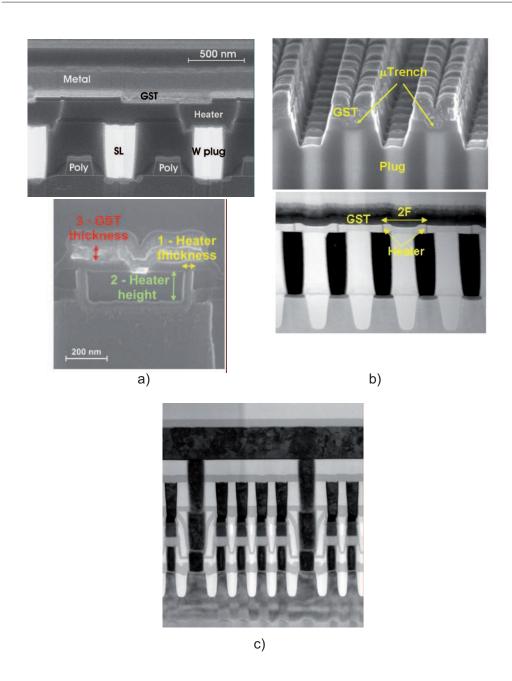

In fact, a PCM memory chip is made of a large number of PCM cells organized in a bi-dimensional array. As opposed to the case of Flash memories, in which the elementary storage consists of a floating-gate transistor, the PCM memory cell is a programmable resistor and, hence, is a two-terminal device. For this reason, a NOR type architecture is adopted as shown in Fig. 1.5(a). Each memory cell consists of a PCM storage element connected to a selection transistor, which can be either an MOS as depicted in Fig. 1.5(b),

Figure 1.5: Architecture of a PCM array (a) and circuit scheme of a PCM cell (b).

or a bipolar device. The gate or the base of all select transistors of the same row are connected to the same word-line, while the TECs of the PCM cells belonging to the same column are connected to the same bit-line. The memory cell is selected by means of row and column decoders that generate the electrical control signals required for read and write operations.

#### 1.2 PCM cell architectures

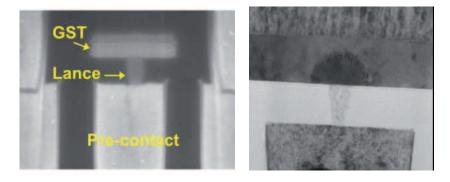

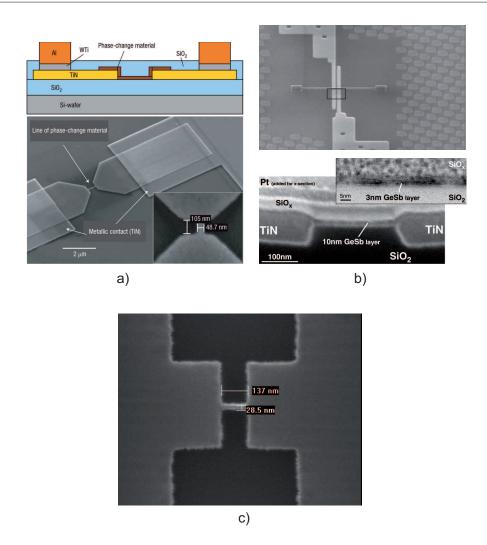

Several memory cell architectures have been investigated to optimize the cell performance, the reproducibility of the device characteristics, and the scalability. Among the vertical structures, the simplest is the lance heater cell (Fig. 1.6), which is composed of a cylindrical heater above which a thin chalcogenide layer is deposed [22]. The required programming current and power depend on the electrical and thermal properties of the heater material and the chalcogenide, on the thermal properties of the surrounding materials and on the sizes of the cell. Since a small heater cross-section enables to reduce the RESET current, a sub-lithographic process is used for the heater

definition. For this reason, this type of cell geometry is referred to as contact minimized architecture. An improved contact minimized architecture is the ring-contact cell that was proposed to improve the reproducibility of the cell characteristics and further reduce the contact area [23, 24] (Fig. 1.7).

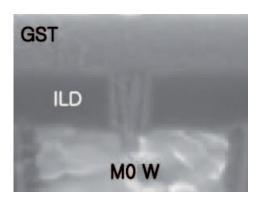

In the above cell architectures, the heater element may be considered the main responsible for the chalcogenide heating. However, some cell architectures have been proposed where Joule heating inside the phase change material (i.e., self-heating) significantly contributes to the active area heating, thus increasing the thermal efficiency of the device and reducing the programming current [25, 27, 28]. Typically, this effect is more relevant in the so-called volume minimized cells such as the pillar or pore cell (Fig. 1.8) [29, 25, 26, 28, 30] and the line cell (Fig. 1.9) which is a lateral structure [31, 32, 33]. In volume minimized architectures, the phase change material is laterally confined within sub-lithographic features, while the BEC and the TEC are quite large structures.

Finally, cell architectures combining the advantages of contact minimized and volume minimized structures have been proposed: the  $\mu$ Ttrench cell [35, 38] and the wall cell [15] (Fig. 1.10). In these cells, the chalcogenide is deposited in a trench which contacts a sidewall heater obtained by means of a sub-lithographic process.

Figure 1.6: Lance heater cell structure realized by IBM/Macronix [22].

Figure 1.7: SEM picture of the ring contact cell realized by Samsung Electronics [23, 24].

$\label{eq:figure 1.8} Figure \quad 1.8: \quad SEM \quad picture \quad of \quad the \quad pillar \quad (or \quad pore) \quad cell \quad structure \quad realized \quad by \quad IBM/Infineon/Macronix \quad PCRAM \quad Joint \quad Project \quad [25] \quad (a) \quad and \quad IBM/Qimonda/Macronix \quad PCRAM \quad Joint \quad Project \quad [26] \quad (b).$

Figure 1.9: SEM picture of the line cell structure realized by Philips Research Laboratories [31] (a), IBM/Qimonda/Macronix PCRAM Joint Project [32] (b), and NXP [34] (c).

## 1.3 Phase change materials

Phase-change materials have been widely employed in optical storage, like CD and DVD, whereas their application to solid-state memories is still under development. Among the alloys that have been studied for application

Figure 1.10: SEM cross sections of the devices realized by STMicroelectronics/Numonyx. The  $\mu$ Trench cell: 180 nm node [35, 36] (a), and 90 nm node [37] (b); the wall cell: 45 nm node [15] (c).

| Parameter                          | Performance affected            |  |  |

|------------------------------------|---------------------------------|--|--|

| Crystallization temperature        | Data retention, SET power       |  |  |

| Crystallization speed              | SET pulse duration, programming |  |  |

|                                    | speed                           |  |  |

| Melting temperature                | RESET power                     |  |  |

| Thermal conductivity in both       | SET and RESET power, efficiency |  |  |

| phases                             | of the cell                     |  |  |

| Resistivity in amorphous and crys- | ON/OFF ratio, read window       |  |  |

| talline phases                     |                                 |  |  |

| Threshold voltage                  | SET voltage and reading voltage |  |  |

Table 1.2: Properties of Phase Change materials

to PCM, the most common is GST  $(Ge_2Te_2Sb_5)$ . However, many chalcogenides allows are still under study with the aim to improve the PCM cell performances by optimizing the alloy composition.

The most important properties of phase-change material for the use in nonvolatile memories are summarized in Table 1.2 [39]. The crystallization temperature,  $T_C$ , is related to the characteristics of the amorphous-to-crystalline phase transition, which determine the power required for the SET operation as well as data retention properties. The crystallization speed affects also the SET time and, thus, the achievable programming speed. GST presents a crystallization temperature of about 145 °C [40]. Among the alternative alloys that present improved data retention performances with respect to GST, it is worth mentioning GeTe [41, 40, 42] ( $T_C \simeq 180^{\circ}$  C), N-doped GeTe [43] ( $T_C \simeq 220 - 270^{\circ}$ C depending on the doping amount), C-doped GeTe [44] ( $T_C \simeq 290 - 330^{\circ}$ C depending on doping amount), oxygen-doped GeSbTe [45], and GeSb [46] ( $T_C \simeq 250^{\circ}$  C).

Regarding the crystalline-to-amorphous transition, the melting temperature,  $T_{melt}$ , is an important parameter which impacts on the power required for amorphization (RESET operation). GST has a melting temperature of about 620°C [47, 42], while  $T_{melt} \simeq 720$ °C for GeTe [42] and N-doped GeTe [43]. The programming power may be reduced by choosing phase change materials having a lower melting point of a lower thermal conductivity, which improves the thermal efficiency of the memory cell.

Finally, the difference of electrical resistivity between the amorphous and the crystalline phase determines the width of the read window and also the ratio between the RESET state and the SET state cell resistance. The resistance ratio is about 3 orders of magnitude for the above mentioned alloys (slightly lower for GST and higher for GeTe [43]).

From the viewpoint of the threshold switching phenomenon, an important parameter is the threshold voltage of the memory cell. This threshold voltage must be low enough to enable low-voltage programming, but sufficiently high to allow the use of a reasonable read voltage which allows relaxing the accuracy of the readout operation.

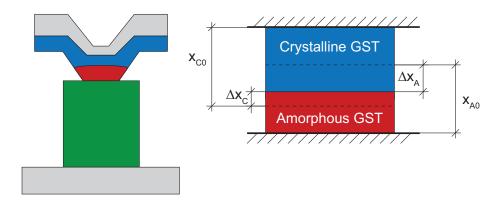

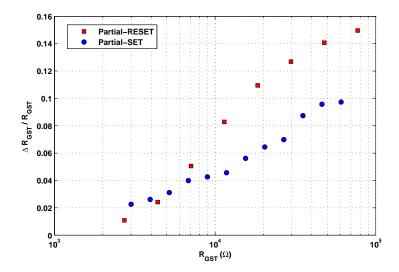

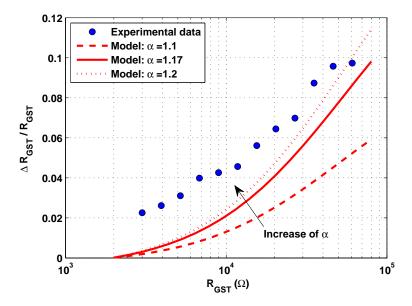

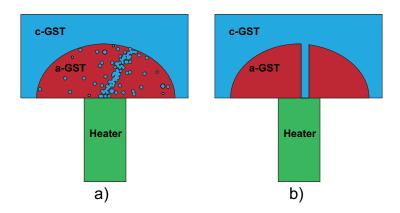

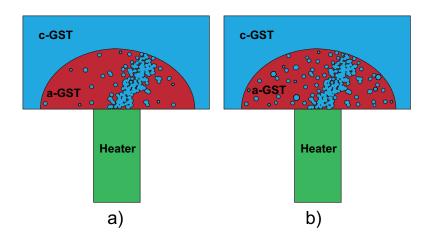

# 2

# Multilevel programming strategies

Multilevel storage in PCM devices [48, 49] requires accurate programming of the cell resistance to predetermined intermediate levels. Two alternative ML programming strategies have been proposed in the literature, namely partial-SET and partial-RESET programming. In the former case, the PCM cell is first programmed to the full-RESET state and, then, partial-SET pulses are applied in order to partially crystallize the amorphous volume [49]. In the latter case, the PCM cell is first programmed to the full-SET state and, then, the GST material is partially amorphized by means of partial-RESET pulses [50]. The distribution of the amorphous and crystalline phases inside the GST layer depends on the programming approach which then determines the properties of the intermediate states from the viewpoint of stability over time.

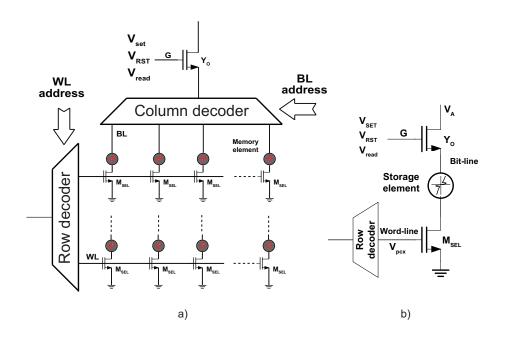

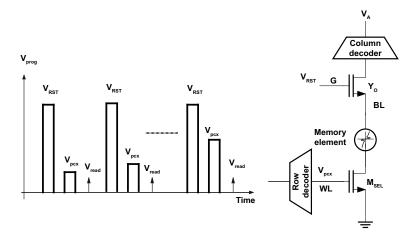

In this Chapter, the characteristics of partial-RESET and partial-SET programming are analyzed and compared to investigate the feasibility of ML storage. All measurements were carried out on a 180-nm 4M-cell PCM experimental chip made of MOS-selcted  $\mu$ Trench cells [51]. The architecture of the considered PCM array and the schematic of the cell biasing circuit are depicted in Figs. 2.1(a) and 2.1(b), respectively.

In voltage programming, the memory cell is biased by applying an adequate voltage level to the selected bit-line (BL) through a high-voltage natural NMOS transistor,  $Y_O$ , which works as a source follower. More specifically, voltage pulses having an amplitude  $V_{RST}$  ( $V_{SET}$ ) are applied to the gate terminal of  $Y_O$  for partial-RESET (SET) programming operations. In voltage programming, device  $Y_O$  is kept in saturation by applying a sufficiently high

Figure 2.1: Architecture of the used PCM array (a) and schematic of the circuit used to program and read memory cells (b).  $M_{SEL}$  and  $Y_O$  are the word-line (WL) select transistor and the bit-line (BL) bias device, respectively.

voltage  $V_A$  to its drain terminal and the addressed word-line (WL) select transistor  $M_{SEL}$  is turned on by applying a high voltage level to its gate ( $M_{SEL}$  works in the triode region). In current programming, transistor  $M_{SEL}$  is operated in its saturation region and, hence, works as a voltage-controlled current source, whereas  $Y_O$  is forced in its triode region by applying a sufficiently high voltage to its gate terminal (5.2 V). The current forced through the PCM cell is controlled by means of the word-line voltage,  $V_{pcx}$ .

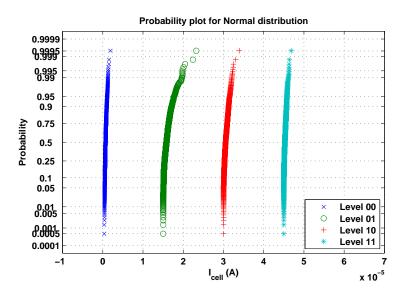

The stored information is read out by sensing the current,  $I_{cell}$ , flowing through the cell (hereinafter referred to as read current) when a suitable read voltage  $V_{read}$  is applied to the gate terminal of  $Y_O$ , which is forced in saturation and operates as a source follower.  $M_{SEL}$  is operated in its triode region with a sufficiently high value of the word-line voltage ( $V_{pcx} = 3$  V), which makes its on-resistance negligible. The read voltage is low enough to prevent un-intentional programming of the GST state (the bit-line voltage is set to about 0.4 V).

Figure 2.2: Partial-RESET programming curve: the volume of amorphous chalcogenide increases with the amplitude of the programming pulse.

In order to measure the read current  $I_{cell}$  with high accuracy, the PCM array can also be operated in direct memory access (DMA) mode. The cell resistance,  $R_{cell}$ , is calculated as the ratio between the read voltage across the cell,  $V_{cell}$ , and  $I_{cell}$ , where  $V_{cell} = V_{read} - V_{GS,Y_0}$  ( $V_{GS,Y_0}$  being the gate-to-source voltage of  $Y_0$ ). By setting  $V_{read}$  to 700 mV,  $V_{GS,Y_0}$  ranges from about 300 mV to 400 mV depending on the value of the cell current and, hence,  $V_{cell}$  varies from 300 mV to 400 mV. Each readout operation is carried out about 1  $\mu$ s after applying the programming pulse due to the used experimental setup. However, this delay can be in principle reduced to about 30 ns while still ensuring us to get rid of resistance recovery phenomenon that determines a remarkable variation of the GST resistance just after the programming operation [52]. The verify operation, where necessary, is performed under the same conditions of readout operation.

Figure 2.3: Sequence of program and read pulses used to obtain the single-pulse (SP) programming curve of PCM cells.

#### 2.1 Partial-RESET programming

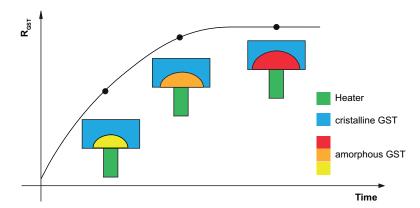

For the considered cell architecture, partial-RESET programming gives rise to a series phase distribution inside the active zone. The volume of chalcogenide amorphized by means of the partial-RESET pulse increases with the pulse amplitude, as schematically depicted in Fig. 2.2, thus determining an increase of the cell resistance.

#### 2.1.1 Single-pulse partial-RESET programming

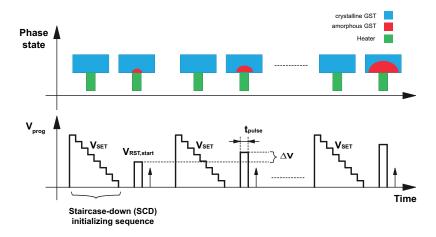

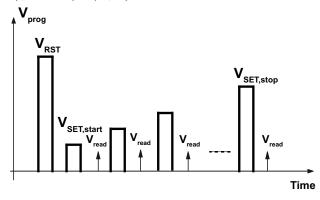

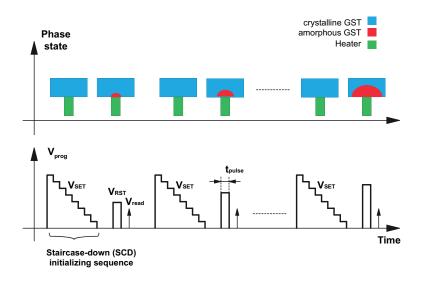

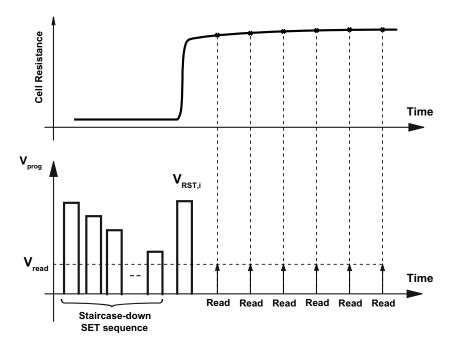

In single-pulse (SP) programming, only one partial-RESET pulse is applied to the PCM cell in its full-SET state to obtain a partial-RESET state. In partial-RESET programming, since the PCM cell is operated in the ON state and far from the threshold switching region, voltage programming and current programming are almost equivalent. In the following, only voltage programming will be considered. The sequence of program and read pulses used to obtain the single-pulse (SP) programming curve, which provides the achieved cell resistance as a function of the used programming voltage, is depicted in Fig. 2.3. The cell is first programmed to the SET state by means of a staircase-down (SCD) initializing sequence [53]. Then, a single partial-

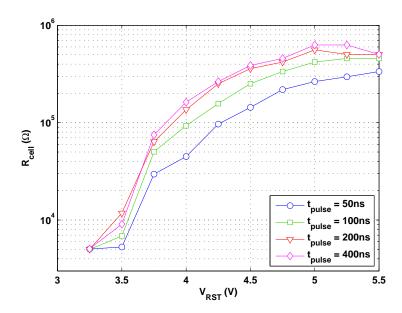

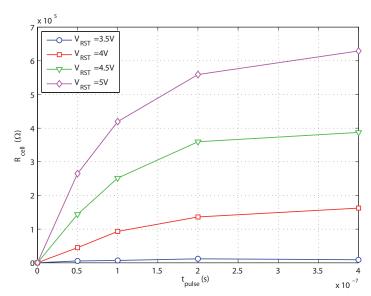

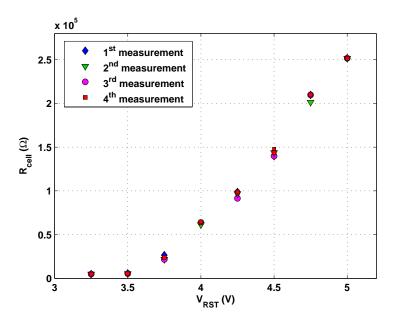

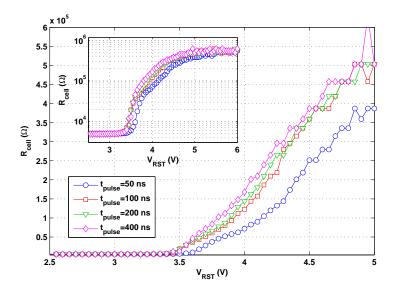

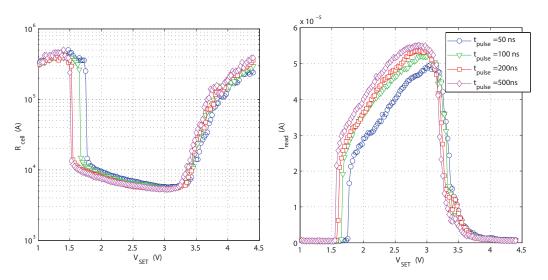

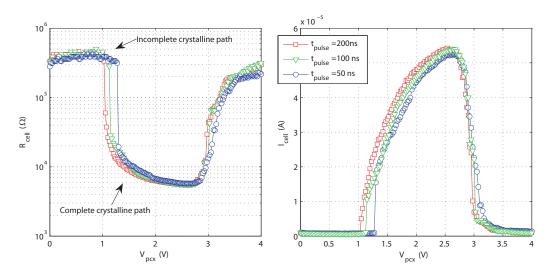

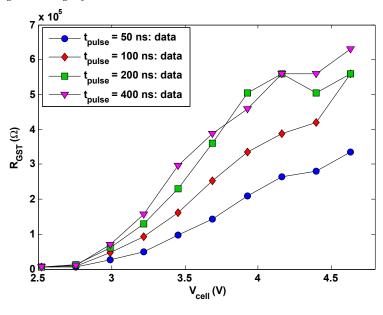

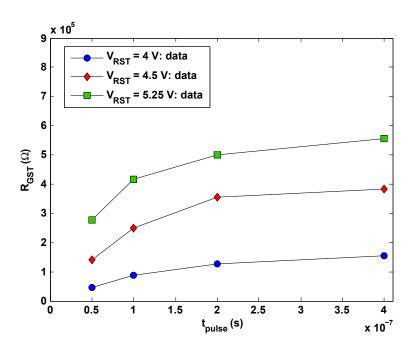

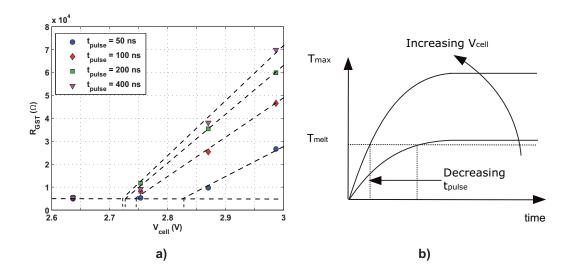

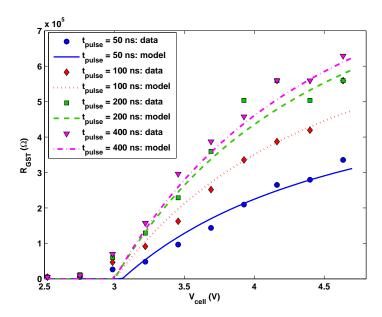

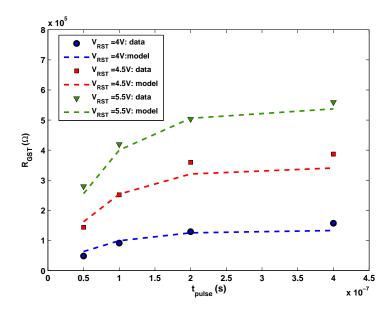

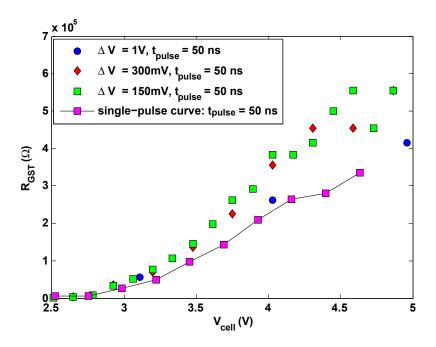

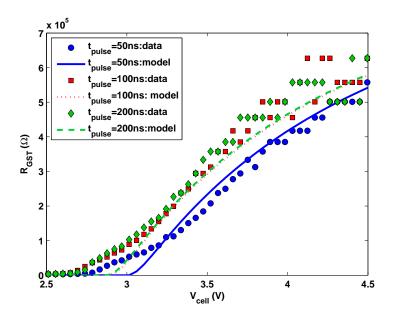

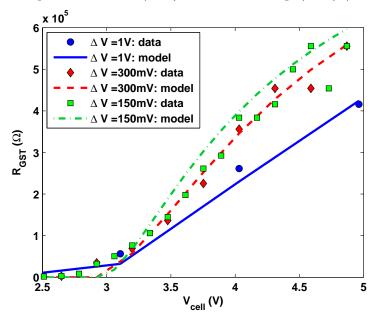

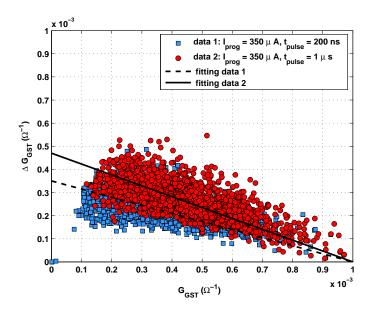

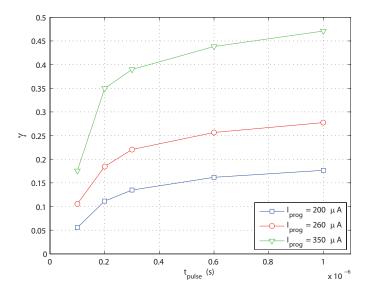

RESET voltage pulse having predetermined amplitude  $(V_{RST})$  and duration  $(t_{pulse})$  is applied, which is followed by a readout operation in DMA mode. The above sequence is repeated with different values of  $V_{RST}$  and  $t_{pulse}$ , in order to obtain programming curves corresponding to different program pulse durations and highlight the impact of the dynamics of the RESET process over the obtained cell resistance for different programming pulse amplitudes. From Fig. 2.4, a significant dependence of the programming curve upon pulse duration is observed. As shown in Fig. 2.5, for any value of  $V_{RST}$ , the programmed cell resistance increases with increasing programming pulse duration, and approaches a saturation level for sufficiently high values of  $t_{pulse}$ . As the saturation resistance increases with  $V_{RST}$ , it is possible to achieve a reasonably high resistance level even with very short-duration pulses, provided that their amplitude is sufficiently high [7]. SP programming curve measurements have been repeated 4 times over the same cell. The obtained results, shown in Fig. 2.6 for the case  $t_{pulse} = 50$  ns, demonstrate a very good reproducibility of the programming curves. These results suggest that the randomness associated with the RESET process is minimum, as opposed to the case of partial-SET programming, where the randomness associated with the crystallization process has a severe impact, as will be shown in Chapter 4. In fact, crystallization takes place when stable crystalline nuclei are formed inside the amorphous array and, then, grow in size. The nucleation process is a stochastic phenomenon which heavily affects the characteristics of partial-SET programming. By contrast, in partial-RESET programming, each cell can be programmed to a predetermined resistance state with good accuracy once its corresponding optimum programming voltage and pulse duration values are determined.

A key aspect to be considered when developing an effective programming algorithm is that, as will be discussed in Section 2.1.3, the optimum voltage  $V_{RST}$  for any target value of cell resistance varies when considering different cells even inside the same array. This behavior suggests to use a Program and Verify technique to obtain the necessary accuracy for multilevel storage.

Figure 2.4: Single-pulse programming curve obtained by means of the programming procedure shown in Fig. 2.3 for different values of  $t_{pulse}$  (50 ns, 100 ns, 200 ns, 400 ns).

Figure 2.5: Dynamics of the RESET process in single-pulse partial-RESET programming for different values of  $V_{RST}$  (3.5 V, 4 V, 4.5 V, and 5 V).

Figure 2.6: Measurements of the single-pulse partial-RESET programming curve repeated 4 times on the same memory cell  $(t_{pulse} = 50 \text{ ns})$ .

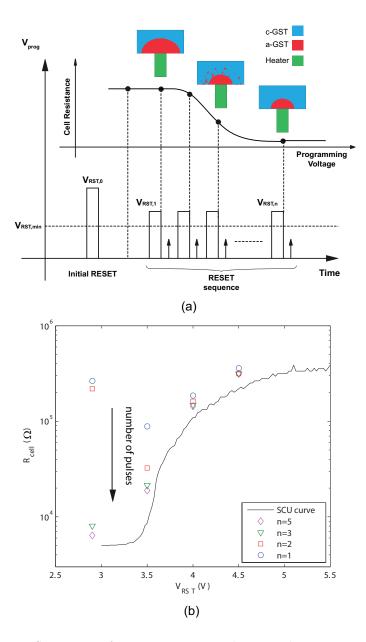

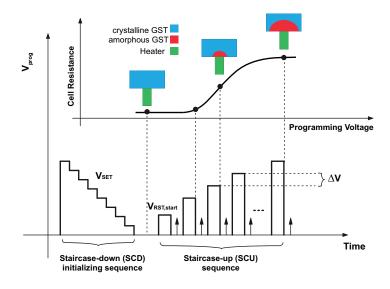

#### 2.1.2 Staircase-up partial-RESET programming

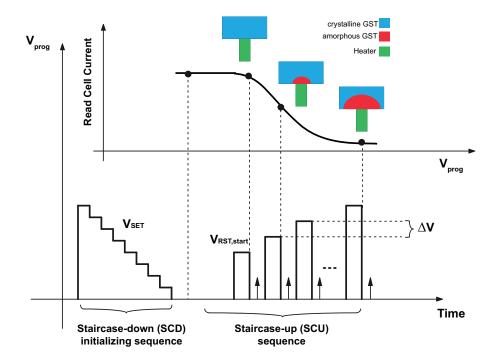

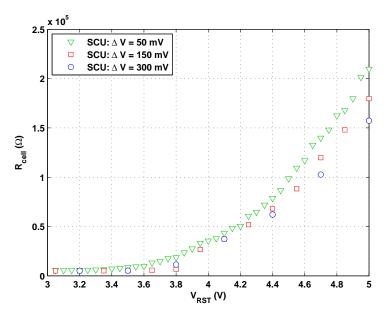

To perform staircase-up (SCU) programming, a staircase-up sequence of partial-RESET voltage pulses (initial amplitude  $V_{RST,start}$ , increment at each step  $\Delta V$ , pulse duration  $t_{pulse}$ ) was applied after a staircase-down (SCD) initializing sequence, as depicted in Fig. 2.7. The read current  $I_{cell}$  was sensed in DMA mode after each programming pulse and the corresponding cell resistance was calculated, thus obtaining the programming curves in Fig. 2.8. The saturation of the programmed resistance for high values of  $V_{RST}$  is high-lighted in the inset of Fig. 2.8. A slight increase of the minimum voltage required for amorphization is apparent when the pulse duration is decreased. Furthermore, the slope of the programming curves increases with increasing values of  $t_{pulse}$ .

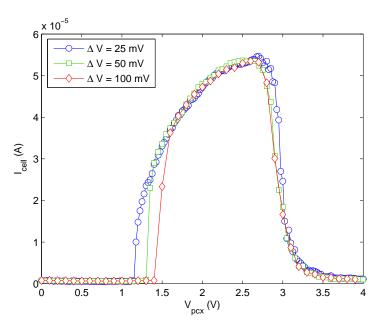

As shown in Fig. 2.9, a similar effect is obtained by decreasing the value of  $\Delta V$ .

The phase state of the memory cell affects the programming operation only when fast pulses are used (for instance, 50 ns in Fig. 2.9), while when

$Figure\ 2.7:\ Sequence\ of\ programming\ pulses\ used\ to\ obtain\ the\ SCU\ partial-RESET$   $programming\ curves.$

Figure 2.8: SCU partial-RESET programming curves obtained on the same cell with  $V_{RST,start}=2.5~V,~\Delta V=50~mV,~and~different~values~of~t_{pulse}~from~50~ns~to~400~ns.$

Figure 2.9: SCU partial-RESET programming curves obtained on the same cell with  $V_{RST,start}=3~V,~t_{pulse}=50~ns,~and~different~values~of~\Delta V$ .

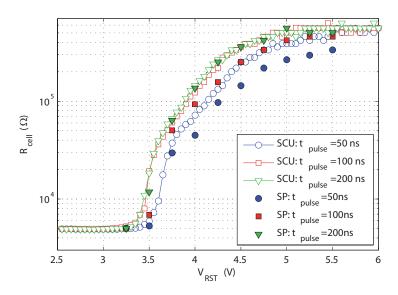

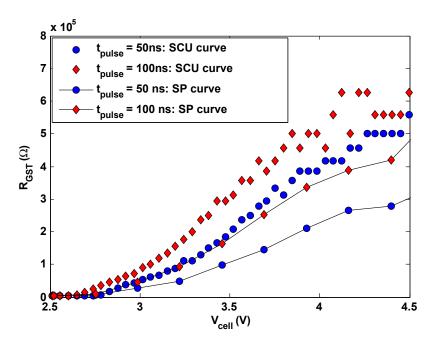

Figure 2.10: Single-pulse programming curve compared to SCU programming curve for different values of  $t_{pulse}$ .

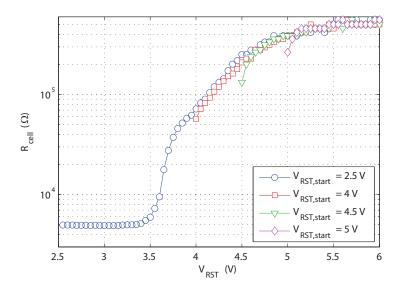

Figure 2.11: Programming curves obtained by means of the SCU algorithm in Fig. 2.7 with different values of  $V_{RST,start}$  ( $t_{pulse} = 50$  ns).

the pulse duration is increased, the obtained state becomes independent from the previous one. This behavior is apparent in Fig. 2.10, where staircase-up programming is compared to SP programming. A significant difference between the programming curves in the two cases can be observed only for low values of  $t_{pulse}$ . For high values of the pulse duration ( $t_{pulse} \geq 200$  ns), the programming curve is substantially independent of the considered programming procedures.

Finally, when SCU programming sequences with different values of the initial RESET voltage,  $V_{RST,start}$  are used, as in Figure 2.11, only few partial-RESET pulses are required to cancel the dependence of the programming curve on the value of  $V_{RST,start}$ . This property is beneficial from the viewpoint of ML programming speed, as will be explained in next Section.

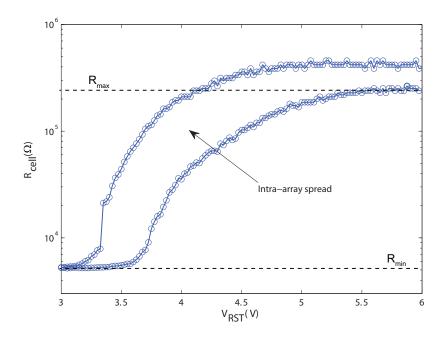

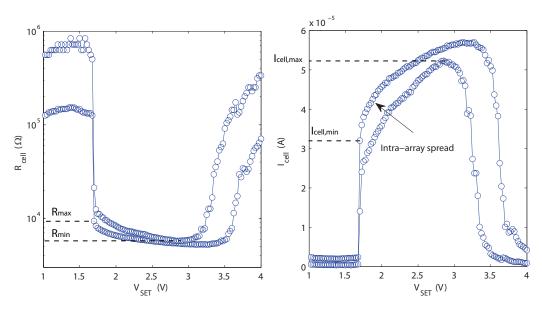

#### 2.1.3 Array analysis of SCU programming

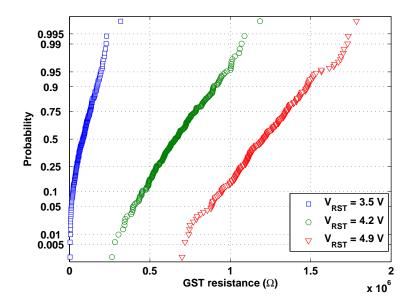

In order to analyze the feasibility of ML partial-RESET programming, the performance of the SCU programming algorithm needs to be evaluated over an array of memory cells. To this end, the sequence of SCU programming pulses in Fig. 2.7 with  $V_{RST,start} = 3 \text{ V}$ ,  $\Delta V = 25 \text{ mV}$ , and  $t_{pulse} = 50 \text{ ns}$  was applied to an array of 1K cells. The obtained programming curves greatly vary from cell to cell (see the highlighted region in Fig. 2.12) due to the intra-array variability of device parameters. In particular, since different cells reach different values of maximum resistance, a remarkable spread in the high resistance value of the programming curve is apparent. Therefore, in our case, the resistance window where programmed levels can be reliably allocated corresponds to the range from  $R_{min} \simeq 5 \text{ k}\Omega$  to  $R_{max} \simeq 200 \text{ k}\Omega$ .

The spread between different cells inside the array makes blind partial-RESET ML programming not applicable. Nevertheless, a Program & Verify (P&V) technique [54, 55] can be adopted to compensate for this spread and improve the accuracy of programmed resistance levels. In Program & Verify, when the read current corresponding to the programmed state decreases below a target value for the considered level, the staircase-up algorithm is stopped. The maximum voltage applied to the cell is named  $V_{RST,stop}$ . Since  $V_{RST,stop}$  depends on the cell characteristics, P&V is also beneficial for compensating the observed intra-array spreads.

Figure 2.12: Spread of the measured SCU partial-RESET programming curves over the considered 1K-cell array with  $V_{RST,start}=3$  V,  $\Delta V=25$  mV, and  $t_{pulse}=50$  ns.

Figure 2.13: Multilevel spacing strategies: (a) linearly-spaced resistance levels, (b) linearly-spaced read current levels, and (c) log-spaced levels.

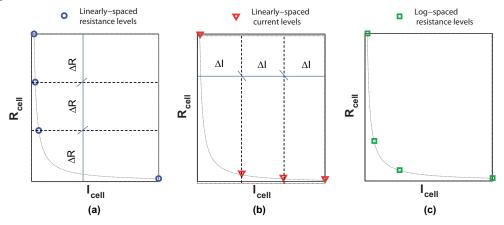

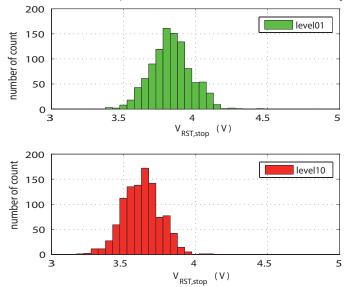

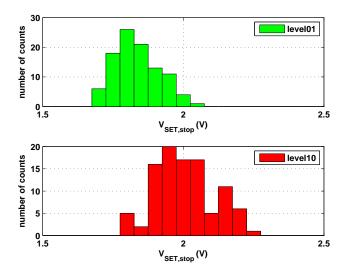

The choice of the spacing between adjacent programmed levels within the available window is driven by trade-off considerations between program and read operations. From the viewpoint of partial-RESET programming, the parameter which is directly controlled when applying a partial-RESET pulse to the cell is the thickness of the obtained amorphous cap that, to a first approximation, determines the cell resistance through a proportionality relationship inside a reasonable resistance range [56]. Then, the intrinsic mechanism of partial-RESET programming suggests to choose equally spaced levels within the available resistance window, as shown in Fig. 2.13(a). In this case, the obtained distributions and the corresponding histograms of  $V_{RST,stop}$  are shown in Fig. 2.14 and 2.15, respectively. However, when adopting a current sensing approach, like in our case, this choice results in current levels very close to one another in the lower part of the read current window, which implies long sensing time to achieve the necessary accuracy.

On the other hand, the optimum choice from the sensing viewpoint, that is to equally space the programmed levels within the available read current window [Fig. 2.13(b)], increases the programming accuracy required for low-resistance levels, which results in longer programming time.

A reasonable trade-off between programming and readout requirements is to choose log-spaced levels inside the available resistance window, as depicted in Fig. 2.13(c). This way, the intermediate read current levels are shifted toward higher values as compared to the case of equally-spaced resistance levels, thus relaxing the sensing accuracy requirements. In addition, the minimum required difference in the cell resistance (and, hence, in the amorphous cap thickness) between adjacent levels is higher with respect to the case of equally spaced read current levels, thus relaxing also the programming accuracy requirements.

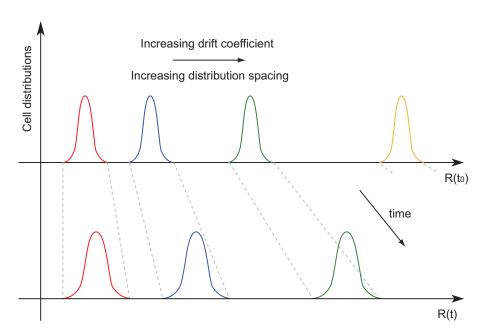

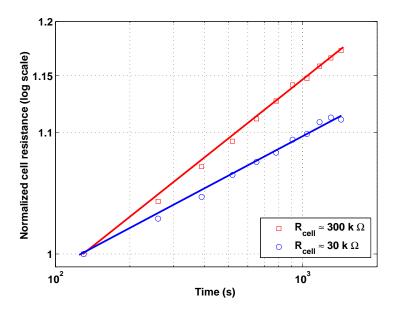

Furthermore, using log-spaced levels is beneficial when considering the effect of the resistance drift phenomenon [57, 58, 59] which determines an increase of the cell resistance over time following a power-law.

In fact, as will be shown in Chapter 4, the drift coefficient increases for increasing values of the cell resistance, leading to a faster dynamics. Then, the resistance shift due to drift during a given time interval after programming increases with the programmed resistance value. This higher shift is

Figure 2.14: Cumulative distributions of the programmed resistance levels in linear resistance spacing. The intermediate levels are obtained by means of the SCU partial-RESET algorithm ( $V_{RST,start} = 2.5 \ V$ ,  $\Delta V = 50 \ mV$ , and  $t_{pulse} = 50 \ ns$ ).

Figure 2.15: Histograms of the maximum programming voltage,  $V_{RST,stop}$ , required to achieve the intermediate levels of Fig. 2.14.

compensated for in log-spaced levels by the inter-level distance, which also increases with the programmed resistance level (high resistance levels are more distant from one another than low resistance levels), as schematically depicted in Fig. 2.16. In this respect, the log-spacing strategy represents an interesting solution to improve reliability, although a drift cancelation technique [52, 59, 60] may still be required when addressing high density ML storage in PCMs.

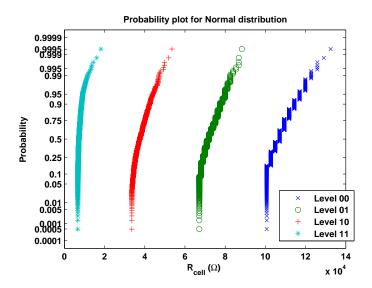

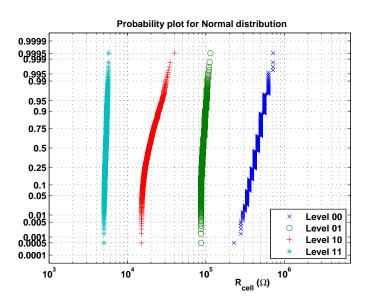

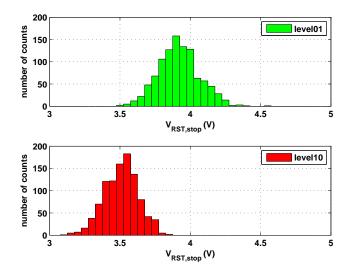

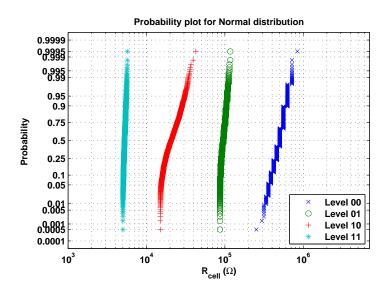

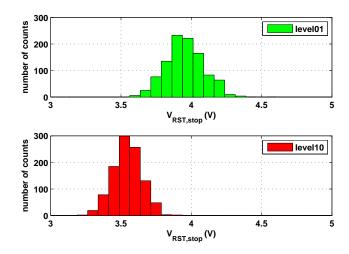

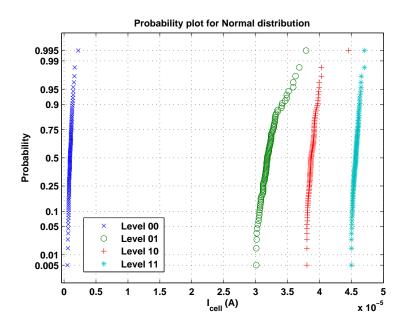

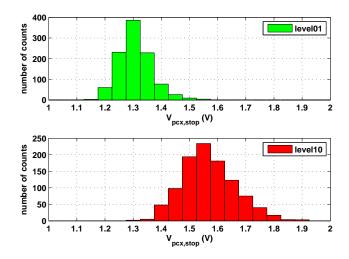

By adopting the log-spacing strategy in Fig. 2.13(c), it was possible to achieve the 4 resistance distributions in Fig. 2.17 (1K cells for each distribution). Level 11 was achieved by means of an SCD SET programming procedure. Level 00 was obtained by means of a single 50-ns RESET pulse whose amplitude (in our case  $V_{RST}=6$  V) was chosen so as to guarantee that the read current of each RESET cell was lower than 1.5  $\mu$ A. The intermediate levels (10 and 01) were achieved by means of the SCU programming sequence in Fig. 2.7 ( $V_{RST,start}=2.5$  V,  $\Delta V=50$  mV, and  $t_{pulse}=50$  ns). The target level for the P&V operation was set to 5  $\mu$ A for level 01 and 21  $\mu$ A for level 10. Figure 2.18 shows the histograms of the highest voltage ( $V_{RST,stop}$ ) of the SCU sequence required to obtain the intermediate levels in Fig. 2.17.

In SCU partial-RESET programming, once the initial programming voltage  $V_{RST,start}$  and the voltage step  $\Delta V$  are chosen, the worst-case programming time linearly increases with the maximum value of  $V_{RST,stop}$  over the array. Indeed, the maximum number of required programming pulses is in practice equal to  $n = \frac{V_{RST,stop} - V_{RST,start}}{\Delta V}$ . Nevertheless, the programming time may be reduced by adapting the value  $V_{RST,start}$  as a function of the target resistance level. In fact, as shown above (Section 2.1.2), the dependence of the SCU programming curve on  $V_{RST,start}$  vanishes after few programming pulses. Then, the value of  $V_{RST,start}$  for each target resistance level may be chosen as the minimum value of  $V_{RST,stop}$  of the corresponding histogram in Fig. 2.18 decreased by  $k\Delta V$ , where k is on the order of few units. This way, the maximum number of required programming pulses and, hence, the worst-case programming time for the considered resistance level turn out to be roughly proportional to the number of bins of the associated histogram of  $V_{RST,stop}$ . The number of bins is higher for the histogram of level 01, which

is therefore the slowest level from the programming viewpoint, whereas it is lower for level 10. This may be ascribed to the lower slope of the  $R_{cell}$  vs  $V_{RST}$  curve for high values of cell resistance due to the resistance saturation effects.

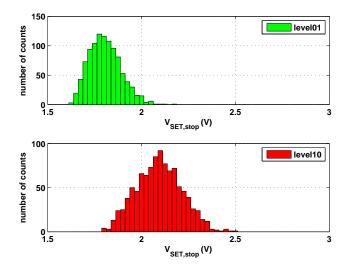

Programming time should be traded with the width of programmed resistance distributions. In fact, an increase in the programming voltage step  $\Delta V$  entails a lower number of SCU pulses on the one side and a lower programming accuracy on the other. To analyze this point, the considered 1K-cell array was programmed by means of the same P&V SCU algorithm as above with the following parameters:  $V_{RST,start} = 2.5 \text{ V}$ ,  $\Delta V = 75 \text{ mV}$ , and  $t_{pulse} = 50 \text{ ns}$ . The verify current levels were set to 3.5  $\mu$ A for level 01 and 20  $\mu$ A for level 10. The obtained distributions and the corresponding histograms of  $V_{RST,stop}$  are shown in Fig. 2.19 and Fig. 2.20, respectively. It can be noticed that the number of pulses necessary to program levels 01 and 10 is significantly decreased with respect to the previous case, where  $\Delta V = 50 \text{ mV}$  (the average number of pulses is now n = 14 for level 01 and n = 10

Figure 2.16: Effect of resistance drift on programmed cell distributions. The shift due to drift increases with the programmed resistance value.

Figure 2.17: Cumulative distributions of the programmed resistance levels in log-spacing: level 01 and level 10 are obtained by means of the P&V SCU algorithm ( $V_{RST,start}=2.5\ V,\ \Delta V=50\ mV,\ and\ t_{pulse}=50\ ns)$ , while level 00 and level 11 are obtained by means of a single RESET pulse ( $t_{pulse}=50\ ns,\ V_{RST}=6\ V$ ) and a SCD procedure, respectively.

Figure 2.18: Histograms of the maximum programming voltage,  $V_{RST,stop}$ , used to obtain resistance levels 01 and 10 of Fig. 2.17.

for level 10). On the other hand, the width of the programmed resistance distributions is slightly increased.

A possible approach to conjugate high programming speed and high accuracy is to use the minimum programming pulse duration (50 ns in our case) and choose a specific value of  $\Delta V$  for each intermediate target resistance level. Once the target width of the intermediate resistance distributions is set, the number of programming steps can be minimized by first determining the minimum  $\Delta V$  required to program level 10 with the desired accuracy. Then, a higher value of  $\Delta V$  may be adopted for level 01 in order to compensate for the larger spread of  $V_{RST,stop}$ .

Another approach to reduce the number of required programming steps is to adopt a bi-directional programming algorithm [61] rather than the SCU algorithm. In partial-RESET SCU programming, the amorphous volume sizes are progressively increased until the desired resistance level is achieved. In the bi-directional approach, the amorphous volume sizes may be either increased or decreased at each programming step in order to rapidly converge to the target resistance value. Since with the bi-directional algorithm, the cell resistance converges to the desired range by overshooting and undershooting around the target value, two verify operations may be required in order to verify that the read current is close enough to the target level (one verify operation is required for the upper boundary and the other for the lower boundary of the resistance range for each programmed level). Then, bidirectional programming needs a more complex verify operation with respect to SCU programming, where the resistance distributions are obtained by only verifying if the read current decreases below a reference value. In fact, the maximum decrease of the read current (i.e., the cell resistance increase) given by a pulse of the SCU sequence is limited and can be reduced by decreasing the voltage step, thus tightening the resistance distributions as shown above.

To analyze the limits of bi-directionality in partial-RESET programming, the measurements shown in Fig. 2.21(a) were performed on a single cell. The PCM cell was first brought into the full-RESET state and, then, a sequence of identical partial-RESET pulses was applied to the device to re-crystallize a portion of the active area and reduce the cell resistance. As shown in Fig.

Figure 2.19: Cumulative distributions of the programmed resistance levels: level 01 and level 10 are obtained by means of the P&V SCU algorithm ( $V_{RST,start}=2.5$  V,  $\Delta V=75$  mV, and  $t_{pulse}=50$  ns), while level 00 and level 11 are obtained by means of a single RESET pulse ( $t_{pulse}=50$  ns,  $V_{RST}=6$  V) and a SCD procedure, respectively.

Figure 2.20: Histograms of the maximum programming voltage,  $V_{RST,stop}$ , used to obtain resistance levels 01 and 10 of Fig. 2.19.

Figure 2.21: Sequence of programming pulses used to investigate the bidirectionality of partial-RESET programming (a) and comparison of the obtained results with the SCU programming curve (b).

2.21(b), the obtained resistance values become closer to the values obtained in SCU programming with increasing number of pulses, which crystallize the region surrounding the GST melted zone.

Furthermore, since the crystallization process must be activated to reduce the amorphous volume size, the crystallization dynamics imposes a lower limit to the programming pulse duration (or to the minimum number of identical pulses) in the bi-directional approach, which impacts on the achievable programming time.

# 2.2 Partial-SET programming

In SCU partial-SET programming, the memory cell first undergoes a full-RESET operation and, then, a sequence of partial-SET programming pulses is applied in order to partially crystallize the initially amorphous chalcogenide. The SCU sequence is applied to the gate of transistor  $Y_0$  for voltage programming, and to the gate of transistor  $M_{SEL}$  for current programming. Unlike partial-RESET programming, partial-SET programming is sensitive to the effects of threshold switching and, thus, different results are obtained when forcing current or voltage to program the memory cell.

The phase distribution achieved after a partial-SET pulse is substantially parallel, with a conductive path that shunts the remaining amorphous phase [62, 63, 64, 65]. Some evidence of incomplete filament formation in partial-SET states has also be provided in the literature [66], but concerning states having very high resistance close to the full-RESET state resistance, that corresponds to a small fraction of the programming window.

In order to better highlight the characteristics of partial-SET programming, in the following study programming curves plotting  $I_{cell}$  versus programming voltage will be provided.

### 2.2.1 Single-pulse programming

To investigate the feasibility of single-pulse programming for partial-SET ML storage, the single-cell programming characteristic (i.e., the curve which provides  $I_{cell}$  as a function of the programming pulse amplitude) was measured by means of the procedure depicted in Fig. 2.22 [67].

Figure 2.22: Sequence of voltage pulses applied to the gate of transistor  $Y_0$  ( $V_{RST}$ ) and to the gate of  $M_{SEL}$  ( $V_{pcx}$ ) during the characterization of the single-pulse programming (SPP) approach. Each current partial-SET pulse has an amplitude higher than the previous one and is preceded by a voltage RESET pulse. After each partial-SET pulse, a read operation is carried out so as to evaluate the read cell current, which allows the programming curve to be obtained.

The cell successively undergoes a voltage RESET operation, a SET operation (voltage pulse amplitude =  $V_{SET}$  applied to the gate of  $M_{SEL}$ ), and a DMA readout operation. The above sequence was repeated while increasing the SET programming pulse amplitude by an amount  $\Delta V$  at any step, until the complete programming curve was obtained. Since a single SET pulse was applied after a RESET pulse to program the cell to an intermediate resistance state, this programming sequence is referred to as single-pulse (SP) programming in the following. More in detail,  $\Delta V$  was set to 25 mV and the time length of each partial-SET program pulse,  $t_{pulse}$ , was varied from 100 ns to 500 ns.

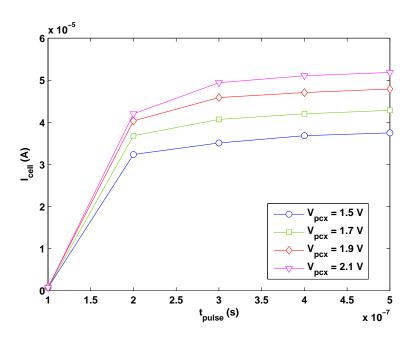

The dependence of the programmed cell current on pulse duration is shown in Fig. 2.23. It can be observed that a pulse length of 100 ns is not sufficient to determine a significant increase of  $I_{cell}$ , even though the programming current for the considered values of  $V_{pcx}$  is higher than the threshold current. A 100-ns pulse turns out to be too short to crystallize a sufficient amount of chalcogenide to obtain a complete crystalline path that shunts the

Figure 2.23: Dependence of  $I_{cell}$  on pulse duration for different values of  $V_{pcx}$ . For the initial RESET operation,  $V_{RST}=5\,$  V and  $t_{pulse}=100\,$  ns.

Figure 2.24: Programming characteristic of a PCM cell when following the partial-SET SP programming approach (program pulse length  $t_{pulse} = 500 \, \text{ns}$ ).

Figure 2.25: Repeated measurements of the programming characteristic of the same PCM cell when following the partial-SET SP programming approach.

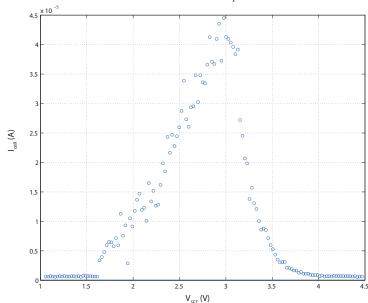

resistance of the remaining amorphous volume (the fraction of crystalline phase inside the amorphous cap is lower than the critical value necessary to achieve a parallel phase configuration). The programming curve of a single cell is shown in Fig. 2.24. It can be noticed that a significant increase of the read cell current with respect to the value in the RESET state takes place when  $V_{SET}$  reaches about 1.6 V. This value is related to the electronic switching phenomenon in amorphous GST [21, 68], which is responsible for a sudden drop of the electrical resistivity of amorphous phase when the voltage across the memory cell exceeds the switching voltage  $V_{th}$ . When the voltage applied across the cell reaches  $V_{th}$ , the programming current raises, thus leading to a significant increase of the temperature inside the GST which strongly activates the amorphous-to-crystalline phase transition.

From Fig. 2.24, the programming characteristic shows a substantially linear average increase of  $I_{cell}$  for increasing values of  $V_{SET}$  (slope  $\Delta I_{cell}/\Delta V_{SET} \simeq 30 \ \mu\text{A/V}$ ). Nevertheless, the random nature of both the amorphization process (during the RESET pulse) and the crystallization process

Figure 2.26: Programming characteristics obtained with the partial-SET SP programming technique for different values of program pulse time length  $t_P$ : 50 ns  $(A, \times)$ , 500 ns (B, +), and 1  $\mu$ s (C, \*).

Figure 2.27: Voltage waveform applied to the gate of transistor  $Y_0$  during a voltage SCU programming routine. After an initial RESET, the cell current is read and, hence, a sequence of program pulses is applied. A read operation is carried out after each program pulse.

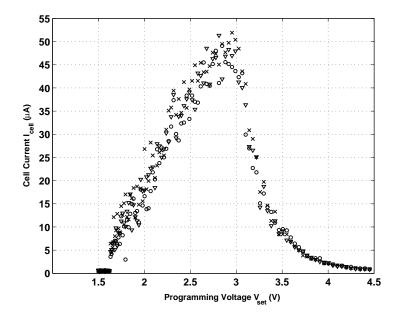

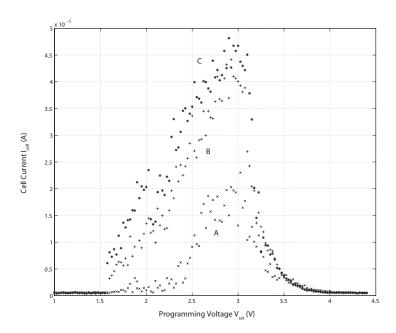

(during the partial-SET pulse) gives rise to a considerable statistical spread of the programmed cell resistance. Thus, if the measurements of Fig. 2.22 are repeated on the same cell a number of times, different programming curves are achieved, as shown in Fig. 2.25. Although the mean characteristic curve of a single cell can in principle be obtained by averaging repeated measurements, the mean programming curve of different cells shows non-negligible differences, due to the fabrication process spreads of the cell geometrical parameters between different chips and even within a memory array in a chip. Then, it is hardly possible to choose the optimum value of the pulse amplitude  $V_{\rm SET}$  to be used for programming a RESET cell to obtain a given target read current level. Furthermore, no convergence towards the target read current value is observed when the programming sequence (RESET pulse followed by a single SET pulse) is repeated on the same cell. As a consequence, SP programming cannot take full advantage of Program-and-Verify technique implementation [54, 55].

From the above considerations, the SP programming algorithm appears to be inadequate to guarantee the high programming accuracy required for ML programming, mainly due to the stochastic nature of the phenomena involved in programming operations and to fabrication process spreads.

#### 2.2.2 Staircase-up voltage programming

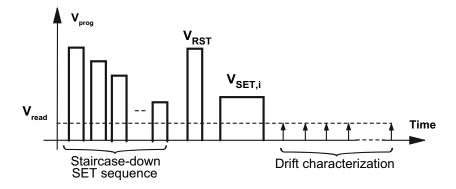

The drawbacks of SP partial-SET programming can be overcome by using a multi-pulse programming algorithm like in partial-RESET approach. In voltage SCU partial-SET programming, a sequence of programming voltage pulses with increasing amplitude is applied to the gate of  $Y_0$ , as shown in Fig. 2.27. The SCU procedure stops when the read current (measured after each programming pulse) exceeds the reference value for the considered level. The minimum and the maximum voltage applied to the gate of  $Y_0$  are named  $V_{SET,min}$  and  $V_{SET,max}$ , respectively.

In this case, the crystallization process takes place inside the active GST volume in a cumulative way, since each pulse increases the PCM cell conductance obtained with the preceding pulse by increasing the cross section of the crystalline path that is dug inside the initially amorphous active volume [62, 63, 64, 65]. As a consequence, the cell resistance gradually decreases as

Figure 2.28: Experimental programming curves when using the voltage SCU algorithm for different values of  $t_{pulse}$  ( $\Delta V=25~mV$ ).

Figure 2.29: Spread of the measured partial-SET SCU voltage programming curves over the considered 1K-cell array ( $t_{pulse} = 100 \text{ ns}$ ).

the number of cumulative SET pulses increases, and the programming curve is therefore inherently monotonic, as is apparent in Fig. 2.28.

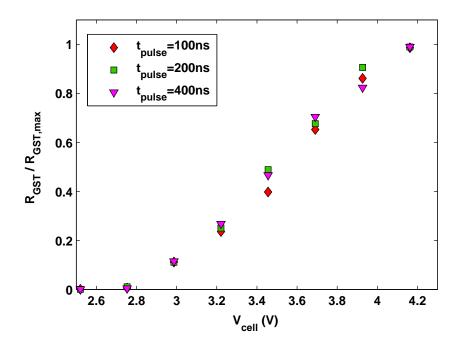

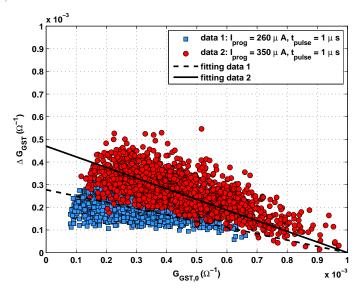

The experimental characterization was carried out with the following parameters:  $V_{SET,start} = 1 \text{ V}$ ,  $\Delta V = 25 \text{ mV}$ , and different values of  $t_{pulse}$  ranging from 50 ns to 500 ns.

It can be noticed that the monotonicity of the programming curve is preserved, although the obtained programming curve still varies from cell to cell (Fig. 2.29). Then, we can implement ML storage by adopting a conventional P&V approach, which allows the programming routine to be stopped when the target cell current value is reached, thereby ensuring the required programming accuracy. This has also been experimentally demonstrated in the literature [13].

From Fig. 2.28, it can be further noticed that a high variation of the read current is achieved with the first effective partial-SET pulses. Since a low slope of the programming curve is desired to program the cell state with high accuracy, it can be observed that voltage programming restricts the available programming range for intermediate levels. In fact, the intermediate levels may be reliably programmed to read current values higher than the highest value of  $I_{cell,min}$  in Fig. 2.29 (for the considered array of cells,  $I_{cell,min} \simeq 30~\mu\text{A}$ ) and lower than the lowest value of  $I_{cell,max}$  (about 50  $\mu$ A for the considered cells), or equivalently, in the range from  $R_{min}$  to  $R_{max}$ ).

#### 2.2.3 Staircase-up current programming

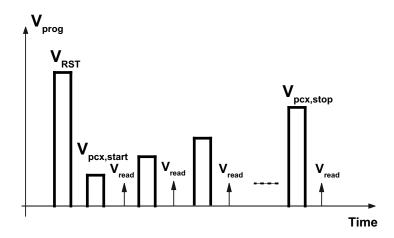

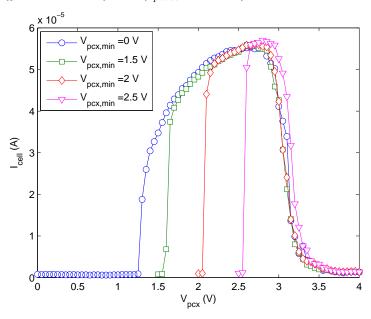

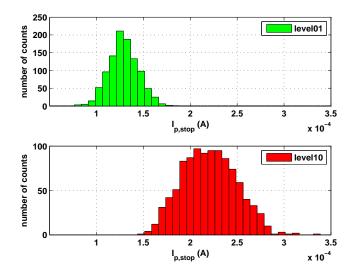

The sequence of program and read pulses used to obtain the SCU current programming curve is shown in Fig. 2.30. After a RESET pulse, a sequence of SCU partial-SET pulses is applied to the cell starting from  $V_{pcx,min}$  (applied to the gate of  $M_{SEL}$ ), each one followed by a readout operation. The SCU procedure is stopped when the read current value exceeds the target value for the considered level. The maximum value of  $V_{pcx}$  is named  $V_{pcx,stop}$ , and corresponds to the programming current value  $I_{p,stop}$ .

The typical shape of a current-driven SCU programming curve is shown in Fig. 2.31 for different values of  $t_{pulse}$  ( $\Delta V = 25$  mV). It can be noticed that there is no significant restriction of the available programming range for the intermediate levels, provided that the pulse duration is sufficiently

Figure 2.30: Programming pulses used to obtain the partial-SET SCU current programming curve. After an initial RESET, the cell current is read and, hence, a sequence of program pulses is applied to the gate of transistor  $M_{SEL}$ . A read operation is carried out after each program pulse.

Figure 2.31: Measured programming curves when using the partial-SET current SCU algorithm for different values of  $t_{pulse}$  ( $\Delta V = 25 \text{ mV}$ ).

Figure 2.32: Programming curves when using the partial-SET current SCU algorithm for different values of  $\Delta V$  ( $t_{pulse}=100$  ns).

Figure 2.33: Programming curves when using the partial-SET current SCU algorithm for different values of  $V_{pcx,min}$  ( $t_{pulse} = 100$  ns,  $\Delta V = 25$  mV).

high. As  $t_{pulse}$  is decreased below a given value (100 ns in our case), the first effective pulse determines a significant increase of  $I_{cell}$ . This behavior is ascribed to the time required to form a complete crystalline path inside the amorphous volume, i.e. to the time required to crystallize a sufficient amount of chalcogenide to obtain a parallel phase configuration. As can be noticed from the plot on the left side in Fig. 2.31, the first pulses determine only a slight decrease of the cell resistance. This suggests that the crystallization process is activated but the crystallized GST is not sufficient to form a complete crystalline path [66]. As soon as a complete path is dug inside the active volume, the resistance suddenly drops.

The critical crystalline fraction for the formation of a complete path is reached at lower pulse amplitudes (i.e., lower temperatures inside the GST volume) if the programming pulse duration compensates for the lower temperature, thus explaining the observed experimental behavior.

It can be further noticed that, as shown in previous Section, an increase of the pulse duration does not help to enlarge the read current programming window in voltage programming. This difference in the cell behavior is ascribed to the threshold switching phenomenon. In fact, in voltage programming, the switching from the OFF to the ON region of the cell V-I curve determines a remarkable increase of the programming current. By contrast, in the current programming approach,  $V_{pcx}$  controls the programming current which, thus, can be gradually increased without any discontinuity.

However, a substantial restriction of the programming range available in current programming appears when  $\Delta V$  is increased, as shown in Fig. 2.32. In this case, the temperature reached during a programming pulse is significantly higher than the temperature obtained during the preceding pulse, thus speeding up the crystallization process. A similar behavior is observed when using the current partial-SET programming algorithm with different values of  $V_{pcx,min}$ , as depicted in Fig. 2.33. Few pulses are needed to dig a complete crystalline path inside the amorphous phase. When the path is complete, the programming current heats the filament and increases its cross-section, thus determining an increase of  $I_{cell}$ . It is worth noticing that, when the crystalline path is formed, the programming curves obtained with different values of  $V_{pcx,min}$  tend to superimpose. This feature enables

Figure 2.34: Cumulative distributions of the read current levels: level 01 and level 10 are obtained by means of the P&V voltage partial-SET SCU algorithm ( $V_{SET,start} = 0 \ V$ ,  $\Delta V = 50 \ mV$ , and  $t_{pulse} = 100 \ ns$ ), whereas level 00 and level 11 are obtained by means of a single RESET pulse ( $t_{pulse} = 100 \ ns$ ,  $V_{RST} = 5.2 \ V$ ) and an SCD procedure, respectively.

Figure 2.35: Histograms of the maximum programming voltage,  $V_{SET,stop}$ , used to obtain resistance levels 01 and 10 in Fig. 2.34.

to reduce the number of programming pulses required to reach the desired current level, as in the case of partial-RESET SCU programming.

## 2.2.4 Array analysis of partial-SET programming

In order to evaluate the effects of the cell parameters spread over the array on partial-SET programming, a sub-array composed of 1K memory cells was considered. First, voltage programming was addressed by applying the sequence of programming pulses shown in Fig. 2.27 to every cell belonging to the array .

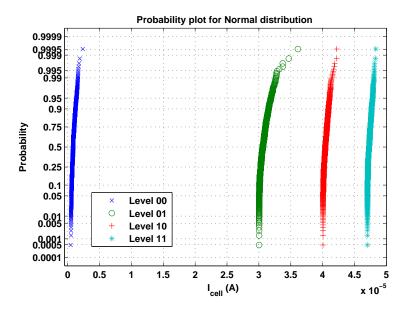

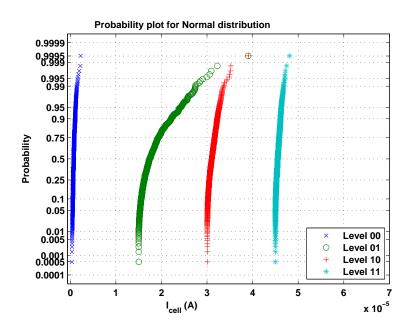

Figure 2.34 shows the obtained cumulative distributions of the programmed levels: levels 00 and 11 were obtained respectively, with a single RESET pulse  $(V_{RST}=5.2~\mathrm{V},\,t_{pulse}=100~\mathrm{ns})$  and a staircase-down procedure, respectively, whereas intermediate levels 01 and 10 were programmed with the voltage SCU partial-SET approach. The chosen programming parameters were the following:  $V_{SET,min}=0~\mathrm{V},\,\Delta V=50~\mathrm{mV},\,\mathrm{and}\,\,t_{pulse}=100~\mathrm{ns}.$  The histograms of the maximum values of the programming voltage  $V_{SET,stop}$  to obtain levels 01 and 10 are shown in Fig. 2.35. It can be noticed that the used  $\Delta V$  is not sufficiently small to achieve the necessary programming accuracy.

In order to obtain separate levels,  $\Delta V$  was decreased to 25 mV. The achieved cumulative distributions of the programmed levels are shown in Fig. 2.36, and the corresponding histograms of  $V_{SET,stop}$  are plotted in Fig. 2.37. Since the width of the histograms is roughly proportional to the time duration of the ML programming procedure, as in the case of partial-RESET programming, the worst case is represented by level 10 (more than 25 pulses). In fact, differently from partial-RESET programming, the slope of the  $I_{cell}$  vs  $V_{SET}$  programming curve is higher for low  $I_{cell}$  (i.e., high  $R_{cell}$ ) values. It can be noticed that levels 01, 10, and 11 are very close one to another (the read current spacing is less than 5  $\mu$ A) due to the reduction of the available range for intermediate levels in voltage programming (see Section 2.2.2). As a consequence of the low read margins, the accuracy constraints on current sensing circuits are very stringent.

In order to relax sensing accuracy requirements, partial-SET SCU current programming can be implemented. However, a suitable value of  $\Delta V$  (voltage

Figure 2.36: Cumulative distributions of the read current levels: level 01 and level 10 are obtained by means of the P&V voltage partial-SET SCU algorithm ( $V_{SET,start} = 0 \ V$ ,  $\Delta V = 25 \ mV$ , and  $t_{pulse} = 100 \ ns$ ), while level 00 and level 11 are obtained by means of a single RESET pulse ( $t_{pulse} = 100 \ ns$ ,  $V_{RST} = 5.2 \ V$ ) and an SCD procedure, respectively.

Figure 2.37: Histograms of the maximum programming voltage,  $V_{SET,stop}$ , used to obtain resistance levels 01 and 10 in Fig. 2.36.

Figure 2.38: Cumulative distributions of the read current levels: level 01 and level 10 are obtained by means of the P&V current partial-SET SCU algorithm ( $V_{pcx,start} = 0 \ V$ ,  $\Delta V = 50 \ mV$ ,  $t_{pulse} = 100 \ ns$ ), whereas level 00 and level 11 are obtained by means of a single RESET pulse ( $t_{pulse} = 100 \ ns$ ,  $V_{RST} = 5.2 \ V$ ) and an SCD procedure, respectively.

Figure 2.39: Histograms of the maximum programming voltage,  $V_{pcx,stop}$ , used to obtain resistance levels 01 and 10 in Fig. 2.38.

Figure 2.40: Cumulative distributions of the programmed resistance levels: level 01 and level 10 are obtained by means of the P&V current partial-SET SCU algorithm ( $V_{pcx,start} = 0 \ V, \ \Delta V = 25 \ mV, \ t_{pulse} = 100 \ ns$ ), whereas level 00 and level 11 are obtained by means of a single RESET pulse ( $t_{pulse} = 100 \ ns, \ V_{RST} = 5.2 \ V$ ) and an SCD procedure, respectively.

Figure 2.41: Histograms of the maximum programming voltage,  $V_{pcx,stop}$ , used to obtain resistance levels 01 and 10 in Fig. 2.40.

increment between adjacent pulses applied to the gate of  $M_{SEL}$  when performing current programming) must be chosen so as to exploit the whole read current window. For instance, the cumulative plot obtained with  $\Delta V = 50$  mV ( $V_{pcx,min} = 0$  V,  $t_{pulse} = 100$  ns) are plotted in Fig. 2.38, and the corresponding histograms of  $V_{pcx,stop}$  are depicted in Fig. 2.39. It can be observed that, although the number of pulses required for programming the intermediate levels is low,  $\Delta V$  is not small enough to achieve a sufficiently narrow distribution for level 01. Then,  $\Delta V$  was reduced to 25 mV, as in the case of partial-SET voltage programming, obtaining the cumulative distributions and the histograms of  $V_{pcx,stop}$  shown in Figs. 2.40 and 2.41, respectively. The width of level 01 distribution is significantly reduced, whereas the number of the programming pulses is roughly doubled.

# Compact modeling of a PCM cell

In both partial-SET and partial-RESET programming analyzed in Chapter 2, the resistance of the intermediate states depends on the distribution of the amorphous and crystalline phases inside the GST layer. In particular, the thickness of the amorphous cap obtained after the partial-RESET operation is a key parameter to control the resistance of the intermediate states in the case of partial-RESET programming. However, the amorphous cap thickness is also important in partial-SET programming since, in this case, it affects the maximum value of the cell resistance and, hence, the programmable window (i.e., the resistance range where all programmed states can be allocated).

The amorphous cap size and, as consequence, the cell resistance, are highly sensitive to the process spreads of device parameters (in particular, of the heater dimensions and the chalcogenide thickness). Optimized cell architectures have been proposed in the literature [23, 24, 69, 26] in order to limit the sensitivity of the programmed resistance values to fabrication process spreads. Nevertheless, since the sensitivity of the programmed resistance to device parameters varies with the pulse amplitude, effective and robust ML programming algorithms should be developed even when considering optimized cell geometries.

In this framework, the aim of this Chapter is to present an analytical model for the partial-RESET operation. Section 3.1 presents a physics-based model of partial-RESET which allows to estimate the expected thickness of the amorphous cap and, thus, the expected cell resistance, as a function of the applied RESET pulse amplitude [70]. Moreover, the model can be used to estimate the effect of fabrication process spreads on the amorphous cap

thickness, showing that the resistance sensitivity to device parameter spreads decreases with increasing amplitude of the RESET pulse.

Section 3.2 extends the analytical model to the dynamic case by taking into account the effects of the partial-RESET pulse duration on the phase-change layer resistance. The dynamic model is able to reproduce the memory cell behavior with good accuracy, considering both single-pulse and staircase-up partial-RESET programming.

The proposed models are validated by comparing the obtained relations with experimental data from the same PCM test chip used to investigate the performance of ML programming algorithms in previous Chapter [35].

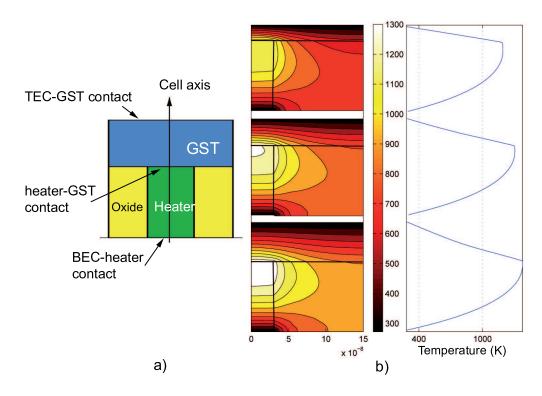

## 3.1 Analytical model of the partial-RESET operation

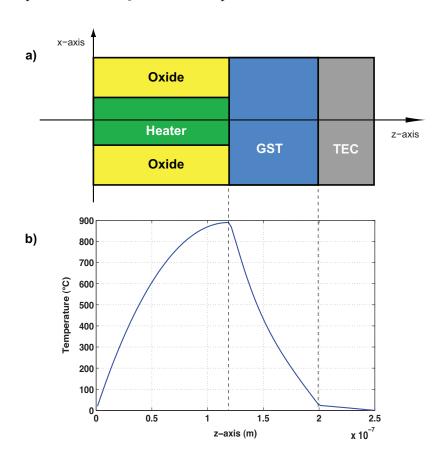

To develop an analytical model capable of estimating the thickness of the amorphous cap obtained after a partial-RESET pulse, the simplified cell geometry of Figure 3.1(a) is considered. The initially crystalline GST amorphizes when heated above the melting point and then quickly cooled down. Thus, the temperature distribution inside the PCM cell is crucial to determine the shape and the thickness of the amorphous cap. The maximum temperature inside the chalcogenide layer, which is achieved very close to the GST-heater interface for the considered  $\mu$ Trench cell architecture [71], is the result of two heating contributions, namely a term  $Q_h$  due to the power generated inside the heater and a term  $Q_{GST}$  generated within the GST (hereinafter, the two terms will be referred to as heater heating and selfheating, respectively). For the cell architecture under study, the self-heating contribution is much lower than the heater-heating contribution, especially when considering high-amplitude RESET pulses which operate the cell in the ON region [64]. In fact, since the crystalline GST shows a semiconductorlike behavior with temperature, the resistance of the fully crystalline layer during the RESET pulse is negligible with respect to the heater resistance  $R_h$ . Even though  $Q_h$  is generated inside the heater volume, for simplicity, we can consider a lumped thermal model in which  $Q_h$  is generated at the heater-GST interface and an equivalent thermal resistance  $(R_{th})$  takes the heater efficiency into account. More specifically,  $R_{th}$  is the lumped thermal

resistance of the memory cell as seen from the heater-GST interface to the thermal ground (which is represented by the top-electrode and the bottom-electrode contacts). Thus, we can simply express the maximum temperature at the GST-heater interface,  $T_{max}$ , as

$$T_{max} = R_{th}Q_h + T_0 = R_{th}\frac{V_{cell}^2}{R_h} + T_0, (3.1)$$

where  $V_{cell}$  is the voltage applied across the PCM cell during the partial-RESET operation and  $T_0$  is room temperature.

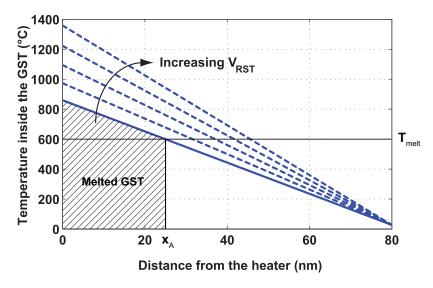

Figure 3.1: Simplified cell geometry for simulating the temperature distribution inside the PCM cell (a) and obtained temperature profile along the AA section of the upper figure (b).

Figure 3.2: Linearized temperature profile inside the GST layer during a RESET operation.

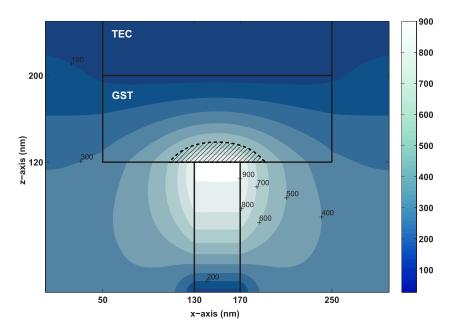

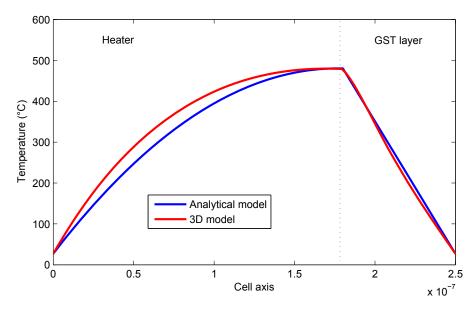

The temperature inside the GST layer decreases along the z-axis from its maximum value to a minimum value (room temperature,  $T_0$ ) at the top electrode contact. In order to evaluate the temperature profile inside the PCM cell, a 3D electro-thermal model of the cell was developed [71]. The simulated temperature along the z-axis of the simplified cell geometry in Fig. 3.1(a) is shown in Fig. 3.1(b). The temperature profile inside the GST decreases almost linearly with the distance from the GST-heater interface, since the heat flow from the heater to the TEC is substantially parallel to the z-axis, as will be shown in the following.

Therefore, the simple linear model depicted in Fig. 3.2 was used to calculate the distance  $z_a$  from the heater-GST interface at which the temperature in the GST is equal to the melting point  $T_{melt}$ , thus obtaining

$$z_a = d \frac{(T_{max} - T_{melt})}{T_{max} - T_0} = d \left( 1 - \frac{(T_{melt} - T_0)R_h}{R_{th}V_{cell}^2} \right), \tag{3.2}$$

where d is the thickness of the GST layer. It is worth noticing that  $z_a$  does depend linearly neither on  $V_{cell}$  nor on the RESET programming power  $(\frac{V_{cell}^2}{R_h})$ : indeed, a sub-linear dependence of  $z_a$  upon  $V_{cell}$  is observed due to

the presence of the TEC, so that  $z_a$  asymptotically approaches d as  $V_{cell}$  approaches infinity.

Let us define  $V_{cell,min}$  as the lowest amplitude of the RESET pulse that, when applied to a PCM cell in the full-SET state, causes a significant increase of the cell resistance (under this condition, the volume of the GST alloy close to the GST-heater interface is heated just above the melting point). The equivalent thermal resistance  $R_{th}$  can be expressed as

$$R_{th} = \frac{(T_{melt} - T_0)R_h}{V_{cell,min}^2} \tag{3.3}$$

and, hence, by substituting Eq. (3.3) in Eq. (3.2), the following expression for  $z_a$  is obtained:

$$z_a = d \cdot \left(1 - \frac{V_{cell,min}^2}{V_{cell}^2}\right) = d \cdot f(V_{cell}), \tag{3.4}$$

where  $f(V_{cell}) = (1 - \frac{V_{cell,min}^2}{V_{cell}^2})$  can be seen as a thickness modulation factor: in fact, the distance  $z_a$  corresponds to the thickness of the amorphous cap obtained after the partial-RESET operation.

Some details about the shape of the amorphous cap are needed to calculate the amorphous cap resistance when the value of  $z_a$  is known. The shape of the obtained amorphous cap is determined by the melting-temperature isotherm obtained inside the GST layer with the used value of  $V_{cell}$ . From the simulated temperature map of Fig. 3.3, which was obtained by means of the above 3D model, it can be noticed that the temperature gradient and, thus, the heat flow just above the heater are roughly parallel to the z-axis. Then, the width of the amorphous cap along the x-axis and, for symmetry, also the width of the cap along the y-axis are much larger than its thickness (z-axis). As a consequence, the amorphous cap resistance depends approximately linearly on  $z_a$ . By neglecting, to a first order, the contribution of the remaining crystalline alloy to the GST layer resistance (which is much lower than the amorphous cap resistance, provided that  $\rho_A z_a \gg \rho_C d$ ,  $\rho_C$  and

$\rho_A$  being the low-field resistivity of the crystalline and the amorphous GST, respectively), the GST resistance is given by

$$R_{GST} \simeq \rho_A \frac{z_a}{A},$$

(3.5)

where A is the area of the contact between the heater and the GST layer. By replacing Eq. (3.4) in Eq. (3.5), the following expression is obtained

$$R_{GST} \simeq R_{max} \cdot f(V_{cell}),$$

(3.6)

where

$$R_{max} = \frac{\rho_A d}{A} \tag{3.7}$$

is the asymptotic maximum resistance, which is achieved in the case of a fully-amorphous GST layer.

Now, Eq. (3.7) can be used to derive the effects of fabrication process spreads on the RESET process: if a RESET pulse of amplitude  $V_{cell}$  is applied

Figure 3.3: Simulated temperature map inside the simplified PCM cell of Fig. 3.1 [71].

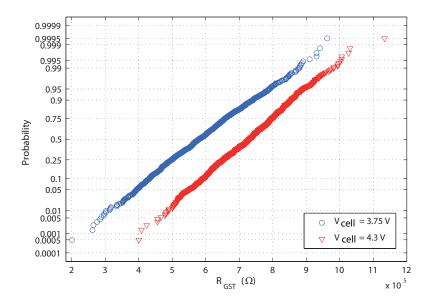

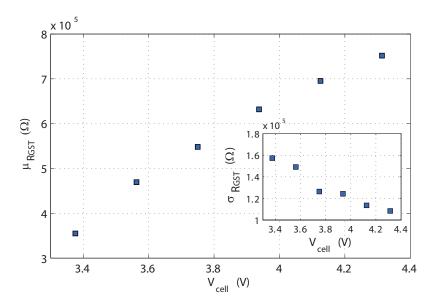

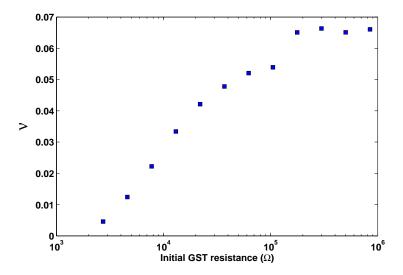

to an array of PCM cells, a Gaussian resistance distribution is obtained, as shown in Fig. 3.4. By considering the possible causes of the resistance spread, the standard deviation,  $\sigma_{R_{GST}}$ , of  $R_{GST}$  can be written as

$$\sigma_{R_{GST}} = \mu_{R_{GST}} \sqrt{\left(\frac{\sigma_{R_{max}}}{\mu_{R_{max}}}\right)^2 + \left(\frac{\sigma_f}{\mu_f}\right)^2},\tag{3.8}$$

where  $\mu_{R_{GST}}$ ,  $\mu_{R_{max}}$ , and  $\mu_f$  are the mean values of  $R_{GST}$ ,  $R_{max}$ , and  $f(V_{cell})$ , respectively, whereas  $\sigma_{R_{max}}$  and  $\sigma_f$  are the standard deviations of  $R_{max}$  and  $f(V_{cell})$ , respectively.

It is worth noticing, from Eq. (3.7), that  $R_{max}$  and, thus,  $\sigma_{R_{max}}$  are independent of the amplitude of the applied RESET pulse. The contribution of  $\sigma_{R_{max}}$  to the spread of  $R_{GST}$  for the considered process can be estimated to be in the order of few hundredths. As will be seen in the following, this contribution is small as compared to the spread introduced by the modulation factor f and, hence, it will be neglected in the following analysis. The sum of the contributions of the remaining process spreads can be modeled by using

Figure 3.4: Normal probability plots of the measured  $R_{GST}$  obtained with two different values of  $V_{cell}$ .

an equivalent normally distributed random variable which, in this case, is  $V_{cell,min}$ . Then, by some hand calculations, the mean value and standard deviation of  $R_{GST}$  can be written as

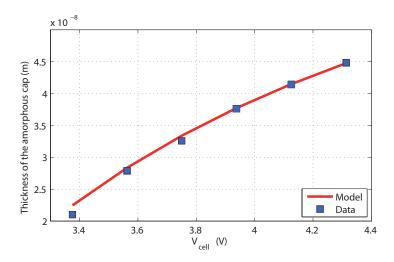

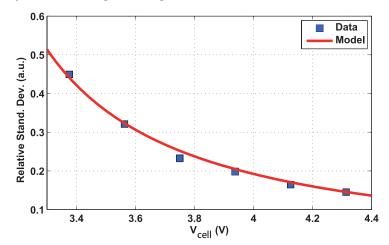

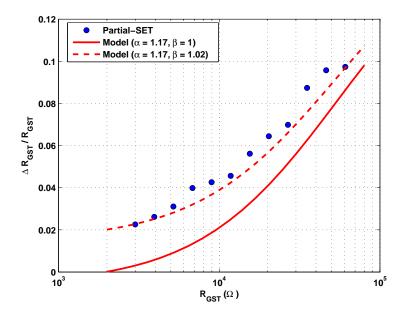

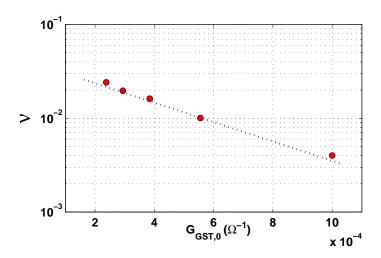

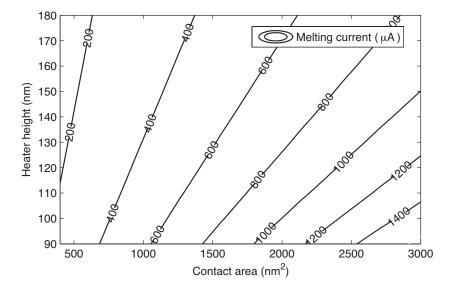

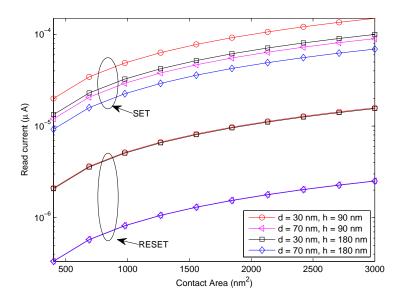

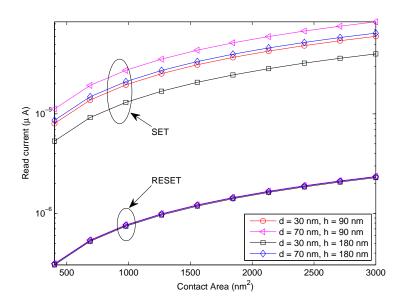

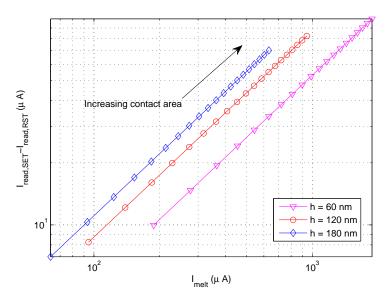

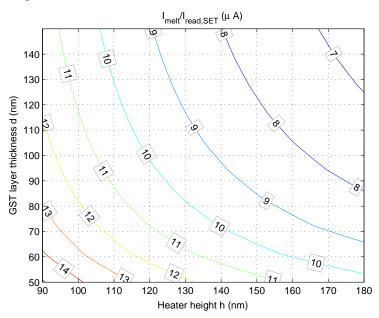

$$\mu_{R_{GST}} \simeq \mu_{R_{max}} \left( 1 - \frac{\mu_{V_{cell,min}^2}}{V_{cell}^2} \right), \tag{3.9}$$